资料下载

×

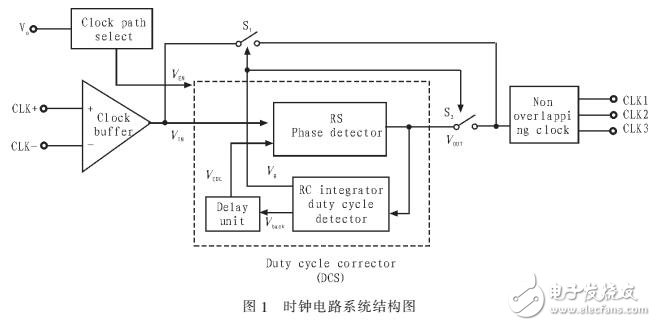

基于改进延迟锁相环的高速低抖动时钟电路的开发与设计

消耗积分:0 |

格式:rar |

大小:0.96 MB |

2017-11-11

时钟产生抖动(jitter)会使发生抖动的时钟信号与未发生抖动的时钟信号在时域上存在偏差,从而使模数转换器的采样频率发生紊乱,最终导致模数转换器采样的不稳定性,使输出信号存在频谱毛刺,导致误码率上升,限制数据结构传输效率。随着输入时钟信号频率的不断增高,由时钟抖动而引起的噪声也逐渐从小频率下的可忽略噪声变换到在高频率下占主导地位而不可忽略,使信噪比(SNR)变小,降低了模数转换的精度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章