资料下载

高速串行信号测试(二)

分析一下抖动的定义,有两个要点:抖动是时间的误差;抖动是实际与理想之间的误差。因此,在测试抖动的时候,我们需要明确这是一个时间量的测试;并且需要找到与之比较的理想信号。

越来越快的数据率意味着承载信息的比特位的时间长度(Unit Interval)会越来越短。对于 1Gbps 的 LVDS 信号,100ps Pk-Pk 的抖动也许不算什么;但是对于 PCIE Gen2.0,100ps pk-pk 的抖动意味着会占据一半的 UI。而 Receiver 数据采样点恰好位于 50%UI 的位置,100ps 的抖动对 PCIE Gen2 是不能接受的。

抖动的类型有很多,不同的定义之间会有很大的差别。通常我们会在“抖动”这个术语前面增加一些限定词:如TIE 抖动、cycle-cycle 抖动、period jitter 等。根据抖动的测试对象不同,我们可以简单的把抖动分为时钟抖动、数据抖动;时钟抖动中可以细分为 period jitter、cycle-cycle jitter;数据抖动主要是 TIE。

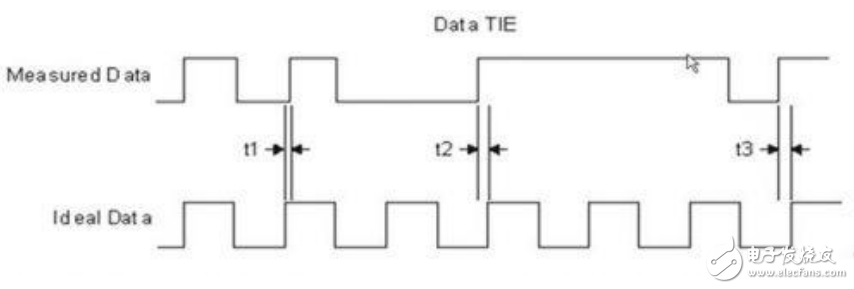

TIE(Time interval Error)顾名思义及时数据信号各个条边沿和理想信号条边沿之间的差异。那么何谓理想的信号呢?我们想象一个数据率为 2.5Gbps 的理想信号,其一个 UI 的宽度是数学意义上的 400ps;实际的测试值多少会偏离这个理想的情况。在实际的工程应用中,理想的数据都是通过 CDR 之后的得到的 clock 来计算的。我们可以回忆一下上一节讨论到的 CDR 的意义。

图:数据 TIE 的定义。t1,t2,t3....为 TIE 样本

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章