资料下载

×

高速ADC在低抖动采样时钟电路设计中的应用

消耗积分:0 |

格式:rar |

大小:0.2 MB |

2017-11-27

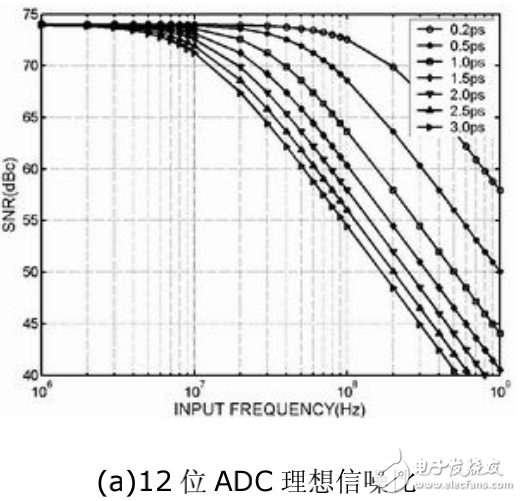

本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

ADC 是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。在A/D 转换过程中引入的噪声来源较多,主要包括热噪声、ADC 电源的纹波、参考电平的纹波、采样时钟抖动引起的相位噪声以及量化错误引起的噪声等。除由量化错误引入的噪声不可避免外,可以采取许多措施以减小到达 ADC 前的噪声功率,如采用噪声性能较好的放大器、合理的电路布局、合理设计采样时钟产生电路、合理设计 ADC 的供电以及采用退耦电容等。本文主要讨论采样时钟抖动对 ADC 信噪比性能的影响以及低抖动采样时钟电路的设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章