资料下载

×

SoC内ADC子系统集成验证挑战

消耗积分:1 |

格式:rar |

大小:0.6 MB |

2017-12-01

现实世界的本质就是模拟。我们需要从周围世界采集的任何信息始终是一个模拟值。但要在微处理器内处理模拟数据需要先将这些数据转换为数字形式。因此,SoC中使用多种不同的ADC(模数转换器)。根据几个参数(即吞吐量、噪声抗扰度及设计复杂性)选择相应类型的ADC。

SoC设计人员不需要了解集成到SoC中的任何IP的复杂深层设计。因此,如果将ADC视为一个黑盒,即使从SoC设计人员的角度来看,在SoC层面仍有许多因素会决定ADC的性能质量。我们必须格外注意这些因素。

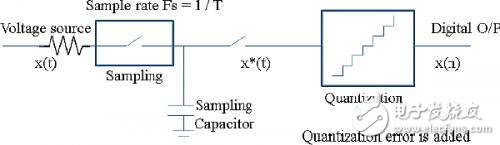

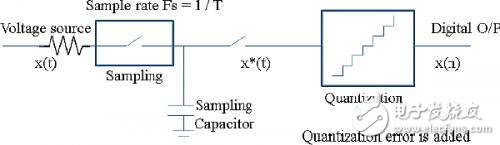

将模拟信号转换成数字数据需要在时间以及幅度上进行离散化。时间离散在采样相位上进行,而幅度离散在量化相位进行。采样通过采样保持电路完成。采样保持电路有一个开关、一个阻抗路径以及一个电容,当开关关闭时在该电容上对电压进行采样。量化简言之是指在一定范围内(由ADC的参考电压控制)将采样值缩放为数字值。采样和量化相位如图1所示。

图1:通用模数转换流程

即使在简单的ADC黑盒示意图中,我们也需要了解其在SoC中的集成知识:

● ADC有多个输入信道,只有一个数字输出。

● 信道之间存在复用,这样,在任何时候ADC都能转换来自于一个信道的数据。

● 采样通过一个时钟进行。

● 任何ADC在其量化相位都使用一个基准。

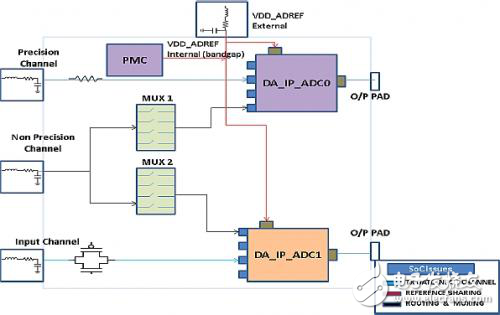

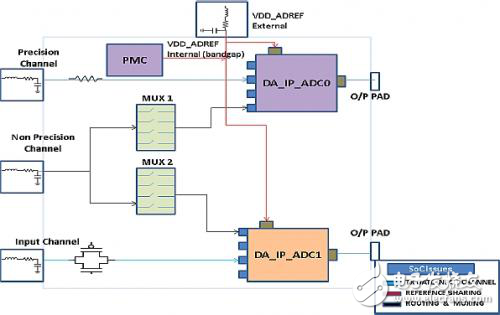

鉴于以上因素,我们便会明白,即使在同一个、甚至非常简单的ADC外部视图中也会有许多设计难点,同时还有许多常见问题。我们将在以下章节中逐一讨论。图2展示了将ADC集成到SoC的一般情况。

图2:ADC到SoC的一般集成

模拟输入信道

在转换的第一个相位,也就是采样相位,输入信道的模拟输入是最重要的。采样电容是ADC设计的组成部分,但是采样遇到的电阻与SoC集成有较大的关联。需要核实一些常见的整合细节。

模拟输入路径的电阻决定采样所需的时间(如果C相同,采样时间将随着R的增加而增加,采样时间等于电容器的充电时间)。采样相位通过一个开关控制。在ADC IP设计的一个可编程寄存器指定的时段内,该开关保持关闭。

SoC设计人员不需要了解集成到SoC中的任何IP的复杂深层设计。因此,如果将ADC视为一个黑盒,即使从SoC设计人员的角度来看,在SoC层面仍有许多因素会决定ADC的性能质量。我们必须格外注意这些因素。

将模拟信号转换成数字数据需要在时间以及幅度上进行离散化。时间离散在采样相位上进行,而幅度离散在量化相位进行。采样通过采样保持电路完成。采样保持电路有一个开关、一个阻抗路径以及一个电容,当开关关闭时在该电容上对电压进行采样。量化简言之是指在一定范围内(由ADC的参考电压控制)将采样值缩放为数字值。采样和量化相位如图1所示。

图1:通用模数转换流程

即使在简单的ADC黑盒示意图中,我们也需要了解其在SoC中的集成知识:

● ADC有多个输入信道,只有一个数字输出。

● 信道之间存在复用,这样,在任何时候ADC都能转换来自于一个信道的数据。

● 采样通过一个时钟进行。

● 任何ADC在其量化相位都使用一个基准。

鉴于以上因素,我们便会明白,即使在同一个、甚至非常简单的ADC外部视图中也会有许多设计难点,同时还有许多常见问题。我们将在以下章节中逐一讨论。图2展示了将ADC集成到SoC的一般情况。

图2:ADC到SoC的一般集成

模拟输入信道

在转换的第一个相位,也就是采样相位,输入信道的模拟输入是最重要的。采样电容是ADC设计的组成部分,但是采样遇到的电阻与SoC集成有较大的关联。需要核实一些常见的整合细节。

模拟输入路径的电阻决定采样所需的时间(如果C相同,采样时间将随着R的增加而增加,采样时间等于电容器的充电时间)。采样相位通过一个开关控制。在ADC IP设计的一个可编程寄存器指定的时段内,该开关保持关闭。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章