资料下载

基于FPGA的曼彻斯特译码电路

信号在传输性能不是很好的信道中传输时,如井下传输系统,如果采用常用的NRZ码传输,会导致信号波形产生较严重畸变,从而导致传输信息错误。而曼彻斯特码作为一种重要的串行数据传输编码方式,由于它消除了NRZ码的直流成分,大幅度减小了传输中波形畸变,因而具有更好的时钟恢复和抗干扰性能,已经在很多场合,如航空电子总线、地震勘探、油井测量、列车运行控制系统等获得广泛应用。经过几十年的发展,曼彻斯特编/解码电路的实现方案主要包括三种:专用编/解码芯片方案、基于微处理器(单片机、DSP)的软件方案嘲吲和基于可编程逻辑器件(CPLD、FPGA)的硬件方案。专用芯片方案存在可编程能力不足、电路集成度低、实现成本高等缺点,新的应用设计已经很少使用;基于微处理器的软件方案,其编/解码处理速度受处理器时钟限制,通常只能应用于通信速率较低(小于1 Mbps)的场合;近年来,随着可编程逻辑器件的飞速发展,基于可编程逻辑器件的硬件方案逐渐成为曼彻斯特编/解码电路的主流实现方案。

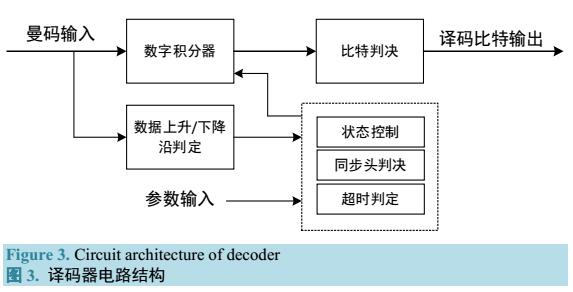

经典的曼彻斯特码译码电路通常采用时钟恢复的方式,利用数字锁相环从接收信号恢复编码时钟,再使周恢复的时钟对接收信号进行同步采集和译码处理,这种译码电路结构复杂,需要消耗较多的电路逻辑单元,提高了电路开发和使用成本。为了降低开发与使用成本,本文设计了一种新型的基于数字积分的译码电路,它利用高频时钟对较低编码速率的信号波形进行积分运算,从而不需要严格的时钟同步即能实现正确解码处理。该译码电路结构简单,消耗电路资源少,且具有较好的抗噪声能力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章