资料下载

如何在FPGA动态局部可重构中进行TBUF总线宏设计

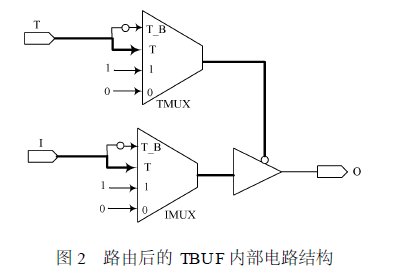

FPGA 动态局部可重构技术通常将系统划分为固定模块和可重构模块,可重构模块与其他模块之间的通信都是通过使用特殊的总线宏实现的。总线宏的正确设计是实现FPGA 动态局部可重构技术的关键。在研究了FPGA 动态局部可重构技术中基于三态缓冲器( Tri2state Buffer ,TBUF) 总线宏结构的基础上,采用Xilinx ISE FPGA Editor 可视化的方法实现总线宏的设计,并借助可重构硬件平台———XCV800 验证板,通过设计动态可重构实验,论证总线宏设计的正确性。

FPGA 动态局部可重构技术是指允许可重构的器件或系统的一部分进行重新配置,配置过程中其余部分的工作不受影响。动态局部可重构缩短了重构的时间,减少了系统重构的开销,提高了系统的运行效率。局部动态可重构技术中通常将系统划分为固定模块和可重构模块。可重构模块与其他模块之间的通信(包括可重构模块和固定模块之间、可重构模块和可重构模块之间) 都是由总线宏实现的。

动态可重构技术在FPGA 中的实现是Xilinx 公司首先提出的,并且提供了相应的开发工具和开发流程。他们从Virtex 系列器件开始支持动态可重构技术,同时他们提供了现成的总线宏文件给动态可重构系统开发者使用,但是它们提供的总线宏设计与软件版本的兼容性很差。Xilinx 提供的总线宏可能因为软件版本的问题会无法正常使用,所以用户需要借助正在使用的版本软件设计总线宏,以实现FPGA 动态局部可重构设计。

在研究总线宏的结构基础上,采用FPGA Editor可视化的方法设计基于TBUF 的总线宏,并通过FP2GA 动态可重构实验验证了该方法的正确性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章