资料下载

×

如何进行一种微功耗轨到轨输出AB类运算放大器设计的资料概述

消耗积分:0 |

格式:rar |

大小:0.86 MB |

2018-12-18

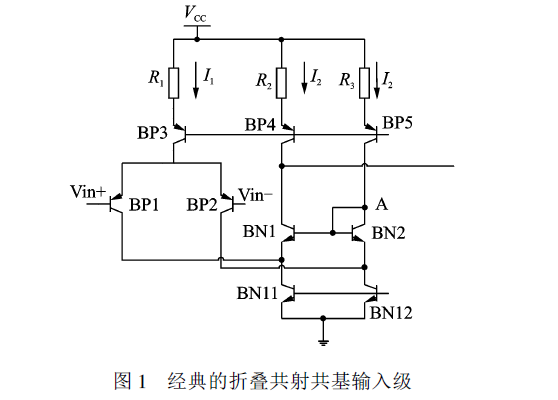

在分析研究AB 类运算放大器的输入和输出级构成原理基础上, 提出一种与信号处理模块的输出端匹配并具有一定负载能力的缓冲器的设计。缓冲器采用了AB 类运放结构, 其输入级采用折叠式共射共基结构, 输出级分别采用PNP 管和NMOS 管作为上拉管和下拉管, 结合电路结构的改进使之具有轨到轨( r ail-to-r ail) 的输出特性和很低的静态电流。设计的电路具有开环增益大、静态功耗小、带宽较高等特点。此运放已在1. 5 um BCD 工艺下实现。测试结果表明, 静态电流仅为8. 5 uA, 闭环带宽达200 kHz, 开环增益为100 dB。

在信号处理模块与负载之间通常需要设置一个缓冲器, 以避免信号处理电路受负载变化的影响, 在提高负载能力的同时保证信号处理的精度。因此, 缓冲器结构必须具备几个特点: 首先, 其输入级与信号处理模块输出端必须匹配; 同时, 其输出级能向后端提供足够强的电流驱动能力, 以适应不同负载的变化; 还要保证系统的带宽和稳定性不受影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章