资料下载

RISC-V读卡器中文手册资料免费下载

RISC-V 自 2011 年推出以来迅速地普及。我们认为一个精简的程序员指南将进一步促进它的发展,并促使新人理解为什么它是一个有吸引力的指令集,以及它与传统指令集架构 (ISA)的不同。

我们的灵感部分来源于其它指令集架构书籍,但我们希望 RISC-V 自身的简洁性能让我们写得比 See MIPS Run 一类 500 多页的详尽书籍少很多。我们把全书的长度控制到了前述的三分之一,至少在这个意义上我们成功了。实际上,介绍模块化 RISC-V 指令集的每个组成部分的十章只用了 100 页——即便为了有助于快速阅读,平均每页用到了一张图片(一共 75 张)。

在解释指令集设计的原理之后,我们将阐述 RISC-V 架构师在设计指令集的时候,如何在过去 40 年的指令集的基础上取其精华,去其糟粕。要评判一个指令集架构,不仅要看它包括了什么,而且要看它省略了什么。

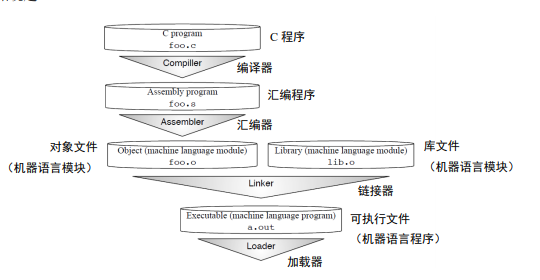

随后我们会按顺序介绍这个模块化架构的每个组成部分。每一章都会包含一个用 RISCV 汇编语言写成的程序,这是为了展示那一章所述的指令的用法,这样有助于汇编语言程序员学习 RISC-V 汇编。有时,我们还会列出用 ARM,MIPS 和 x86 写成的同样的程序,从而突出 RISC-V 在简洁性,以及成本、功耗、性能方面的优势。

为了增加本书的趣味性,我们在页边加入了将近 50 个侧边栏,这里面放了一些有关书中内容的评论,希望它们能带来一些乐趣。我们还在页边放了大约 75 个图片,用于展示设计良好 ISA 的例子。(我们充分利用了侧边的空间!)最后,对于那些愿意钻研的读者,我们在全书中加入了大概 25 段补充说明。如果你对某个主题感兴趣,可以深入研究这些可选部分。略过这些部分不会影响对书中的其他内容的理解,所以如果你对他们不感兴趣的话,尽管跳过它们。对于计算机体系结构爱好者,我们援引的 25 篇论文和书籍能够开阔你的视野。在写这本书的过程中,我们从它们当中学到了很多东西!

RISC-V(“RISC five”)的目标是成为一个通用的指令集架构(ISA):

⚫ 它要能适应包括从最袖珍的嵌入式控制器,到最快的高性能计算机等各种规模的处理器。

⚫ 它应该能兼容各种流行的软件栈和编程语言。

⚫ 它应该适应所有实现技术,包括现场可编程门阵列(FPGA)、专用集成电路(ASIC)、全定制芯片,甚至未来的设备技术。

⚫ 它应该对所有微体系结构样式都有效:例如微编码或硬连线控制;顺序或乱序执行流水线; 单发射或超标量等等。

⚫ 它应该支持广泛的专业化,成为定制加速器的基础,因为随着摩尔定律的消退,加速器的重要性日益提高。

⚫ 它应该是稳定的,基础的指令集架构不应该改变。更重要的是,它不能像以前的专有指令集架构一样被弃用,例如AMD Am29000、Digital Alpha、Digital VAX、 Hewlett Packard PA-RISC、Intel i860、Intel i960、Motorola 88000、以及Zilog Z8000。

RISC-V的不同寻常不仅在于它是一个最近诞生的指令集架构(它诞生于最近十年,而大多数其他指令集都诞生于20世纪70到80年代),而且在于它是一个开源的指令集架构。与几乎所有的旧架构不同,它的未来不受任何单一公司的浮沉或一时兴起的决定的影响(这一点让许多过去的指令集架构都遭了殃)。它属于一个开放的,非营利性质的基金会。RISC-V基金会的目标是保持RISC-V的稳定性,仅仅出于技术原因缓慢而谨慎地发展它,并力图让它之于硬件如同Linux之于操作系统一样受欢迎。图1.1列出了RISC-V基金会最大的企业成员,作为其活力的证明。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章