资料下载

×

10~37 GHz CMOS四分频器的设计方案

消耗积分:1 |

格式:rar |

大小:0.5 MB |

2017-11-17

1 引言

随着通讯技术的迅猛发展,人们对通讯系统中单元电路的研究也越来越多。而分频器广泛应用于光纤通讯和射频通讯系统中,因此,高速分频器的研究也日益受到关注。分频器按实现方式可分为模拟和数字两种。模拟分频器可由注进锁定等结构实现,一般具有工作频率高、功耗低等优点,但是分频范围较小,芯片面积较大。数字分频器基于触发器结构,一般分频范围较宽,芯片面积较小,但相对于模拟分频器其工作频率较低,功耗较大。这里采用UMC 0.13um的CMOS工艺(其特征频率fT约100 GHz),在电源电压为1.2V时,实现一个高速、宽分频范围的数字四分频器。

2 电路设计

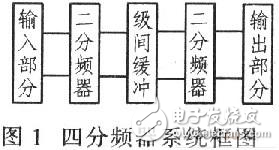

图1为四分频器的系统框图。它由两个二分频器级联而成。为了实现级间隔离和电平匹配,在两个二分频器之间加进级间缓冲电路。为便于区分这两个分 频器,将前一个二分频器称为高速二分频器,后一个二分频器称为低速二分频器。由于要测试电路,需考虑输进和输出端口的阻抗匹配。为解决这些题目,电路中设 计输人和输出部分。输进部分除实现输进阻抗匹配外,还要提供直流偏置。输出部分用以保证测试时的阻抗匹配以及得到一定的输出信号幅度。

2.1 二分频器

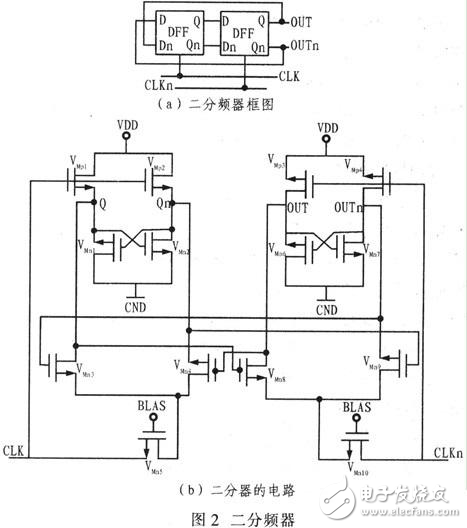

这里采用的二分频器为全差分的共栅动态负载结构,其框图和电路图如图2a和图2b所示。

该二分频器由两个相同的相互交叉耦合的D触发器构成,其中CLK和CLKn为一对差分输进信号。由于两个触发器完全相同,下面仅以图2b中左边 的触发器为例进行分析。当CLK为低电平时,电路工作在采样模式,开关管VMa5导通,输进对管VMn3、VMn4用于采样输进信号,PMOS负载管 VMp1、VMp2工作在线性区,其导通电阻很小,相应的时间常数RC就较小,从而使得输出结点Q,Qn的状态转换时间较短; 当CLK为高电平时,电路工作在保持模式,开关管VMn5截止,PMOS负载管VMp1、VMp2工作在截止区,相应的时间常数很大,而NMOS的交叉耦 合对管VMn1、VMn2形成正反馈,在保持模式下用于维持触发器的输出状态,在采样模式下加快输出节点的状态转换速度。因此该主从结构的触发器形成一个 二分频器。动态负载技术极大地进步了分频器的工作速度。

本文目的是设计高速分频器,因此其工作速度是考虑的首要题目。触发器中决定工作速度的主要因素是输出节点的总电容。同样以图2b中左边的触发器 为例说明,考虑其中一个输出节点Qn相应的总电容,包括与该输出节点相连的所有器件的电容以及它们两者之间连线上的寄生电容。因此在进行电路参数设计和版 图设计时,应减少这些电容。在设计两个二分频器电路参数时,固然两者拓扑结构一样,但由于侧重点不同,所以参数设计并不相同。高速二分频器着重进步其工作速度,因此应尽可能地减少输出节点的电容。

而低速二分频器的工作速度为高速二分频器的一半,故速度不是考虑的主要题目。因此在对低速二分频器电路参数设计 时,在满足二分频的条件下应着重降低其功耗。另外分频器的输出电压摆幅应从两方面考虑:首先输出电压摆幅过大,则充、放电过程持续时间会增加,输出电压摆 幅过小,则无法驱动后续电路。而决定输出电压幅度的主要因素为在保持模式下动态负载管的电阻,因此在设计电路时应进行折衷考虑,仔细调整各管子的参数。在 版图设计时,对于管子宽度比较大的应尽量使用叉指结构,同时应特别留意图2中的4条交叉耦合线应尽可能短,尤其是高速二分频器中的4条交叉耦合线对分频器 的工作速度有很大的影响。

随着通讯技术的迅猛发展,人们对通讯系统中单元电路的研究也越来越多。而分频器广泛应用于光纤通讯和射频通讯系统中,因此,高速分频器的研究也日益受到关注。分频器按实现方式可分为模拟和数字两种。模拟分频器可由注进锁定等结构实现,一般具有工作频率高、功耗低等优点,但是分频范围较小,芯片面积较大。数字分频器基于触发器结构,一般分频范围较宽,芯片面积较小,但相对于模拟分频器其工作频率较低,功耗较大。这里采用UMC 0.13um的CMOS工艺(其特征频率fT约100 GHz),在电源电压为1.2V时,实现一个高速、宽分频范围的数字四分频器。

2 电路设计

图1为四分频器的系统框图。它由两个二分频器级联而成。为了实现级间隔离和电平匹配,在两个二分频器之间加进级间缓冲电路。为便于区分这两个分 频器,将前一个二分频器称为高速二分频器,后一个二分频器称为低速二分频器。由于要测试电路,需考虑输进和输出端口的阻抗匹配。为解决这些题目,电路中设 计输人和输出部分。输进部分除实现输进阻抗匹配外,还要提供直流偏置。输出部分用以保证测试时的阻抗匹配以及得到一定的输出信号幅度。

2.1 二分频器

这里采用的二分频器为全差分的共栅动态负载结构,其框图和电路图如图2a和图2b所示。

该二分频器由两个相同的相互交叉耦合的D触发器构成,其中CLK和CLKn为一对差分输进信号。由于两个触发器完全相同,下面仅以图2b中左边 的触发器为例进行分析。当CLK为低电平时,电路工作在采样模式,开关管VMa5导通,输进对管VMn3、VMn4用于采样输进信号,PMOS负载管 VMp1、VMp2工作在线性区,其导通电阻很小,相应的时间常数RC就较小,从而使得输出结点Q,Qn的状态转换时间较短; 当CLK为高电平时,电路工作在保持模式,开关管VMn5截止,PMOS负载管VMp1、VMp2工作在截止区,相应的时间常数很大,而NMOS的交叉耦 合对管VMn1、VMn2形成正反馈,在保持模式下用于维持触发器的输出状态,在采样模式下加快输出节点的状态转换速度。因此该主从结构的触发器形成一个 二分频器。动态负载技术极大地进步了分频器的工作速度。

本文目的是设计高速分频器,因此其工作速度是考虑的首要题目。触发器中决定工作速度的主要因素是输出节点的总电容。同样以图2b中左边的触发器 为例说明,考虑其中一个输出节点Qn相应的总电容,包括与该输出节点相连的所有器件的电容以及它们两者之间连线上的寄生电容。因此在进行电路参数设计和版 图设计时,应减少这些电容。在设计两个二分频器电路参数时,固然两者拓扑结构一样,但由于侧重点不同,所以参数设计并不相同。高速二分频器着重进步其工作速度,因此应尽可能地减少输出节点的电容。

而低速二分频器的工作速度为高速二分频器的一半,故速度不是考虑的主要题目。因此在对低速二分频器电路参数设计 时,在满足二分频的条件下应着重降低其功耗。另外分频器的输出电压摆幅应从两方面考虑:首先输出电压摆幅过大,则充、放电过程持续时间会增加,输出电压摆 幅过小,则无法驱动后续电路。而决定输出电压幅度的主要因素为在保持模式下动态负载管的电阻,因此在设计电路时应进行折衷考虑,仔细调整各管子的参数。在 版图设计时,对于管子宽度比较大的应尽量使用叉指结构,同时应特别留意图2中的4条交叉耦合线应尽可能短,尤其是高速二分频器中的4条交叉耦合线对分频器 的工作速度有很大的影响。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(1)

发评论

-

ljwcoke

2020-11-09

0 回复 举报下载不起.......... 收起回复

ljwcoke

2020-11-09

0 回复 举报下载不起.......... 收起回复

- 相关下载

- 相关文章