资料下载

如何低成本实现AES密码算法的硬件

现代社会的信息化和网络化给人们的生活带来了方便快捷,但随之而来的信息安全隐患也日益明显,加密技术则是解决这一问题的有效方法。2001年11月26日,美国国家标准技术研究所(NIST)正式批准Rijndael算法为高级加密标准AES。AES密码算法的加密速度快,安全级别高,已经成为加密各种形式的电子数据的实际标准。目前,针对AES密码算法的加密技术已成为研究热点。论文提出了一种低成本的AES密码算法的硬件实现方法,并且使用FPGA器件实现了具体的设计方案,最终设计了一个基于FPGA的AES加密芯片。

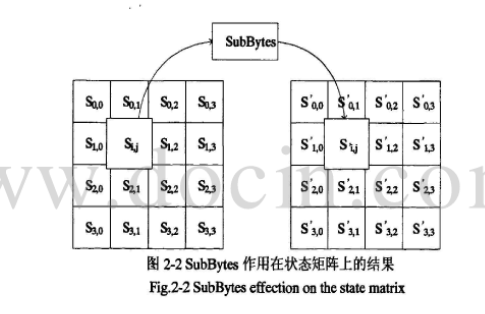

论文首先提出了AES密码系统的体系结构框架。系统采用非流水线结构实现了ECB非反馈和CBC反馈两种工作模式,提高了系统的可配置性,满足了实际工作的需要。此外,在算法的具体实现过程中,采用了直接解密的算法结构,通过可配置的S盒和优化的逆列混合变换,部分消除了加密、解密硬件结构的差异,达到了减少硬件资源的设计目标。

然后,设计中使用VerilogHDL硬件描述语言对上述系统结构框架进行建模。根据相关文献提供的测试数据,采用ModelSim工具对系统的各个模块以及整个系统进行了仿真验证,并且采用Altera公司的QuartusⅡ开发工具完成了系统的综合编译。综合结果表明该AES密码系统基本达到了低成本的预期设计目标,在满足加密、解密速度的基础上,尽可能地减少了硬件资源的消耗,实现了规模和速度的平衡。

最后,将上述综合编译后生成的配置文件下载到Cyclone EP1C12Q240C8器件中,完成了FPGA的配置下载过程,从而完整地实现了AES密码系统的设计过程,开发了一片基于FPGA的AES加密芯片。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章