资料下载

使用硬件描述语言实现数字秒表的设计资料说明

秒表共有6个输出显示,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应,6个计数器的输出全都为BCD码输出,这样便于和显示译码器的连接。当计达60分钟后,蜂鸣器鸣响10声。除此之外,整个秒表还需有一个启动信号和一个归零信号,以便秒表能随意停止及启动。秒表的逻辑结构较简单,它主要由显示译码器、分频器、十进制计数器、六进制计数器。四个10进制计数器:用来分别对百分之一秒、十分之一秒、秒和分进行计数;两个6进制计数器:用来分别对十秒和十分进行计数;分频器:用来产生100Hz计时脉冲;显示译码器:完成对显示的控制。根据电路持点,用层次设计概念将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口。按适配划分后的管脚定位,同相关功能块硬件电路接口连线。用VHDL语言描述所有底层模块。清零信号为异步清零。当最高位记到6时停止计数显示译码器全部显示零。按下复位按钮后继续计数。

实验设计原理:

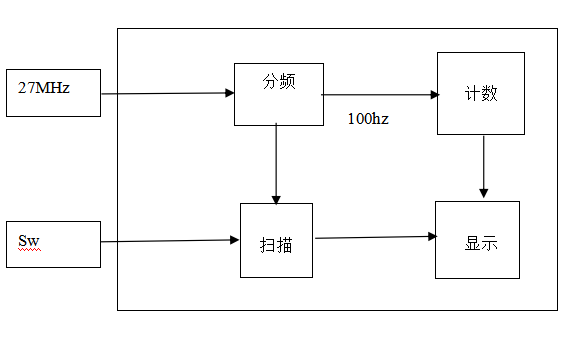

(1)秒表的逻辑结构较简单,它主要由十进制计数器、六进制计数器、分频器、数据选择器、和显示译码器等组成。在整个秒表中最关键的是如何获得一个精确的100HZ计时脉冲,除此之外,整个秒表还需有一个启动信号和一个清零信号,以便秒表能随意停止、启动以及清零复位。

(2)秒表有共有6个显示输出数据,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应。6个计数器的输出全都为BCD码输出,这样便与同显示译码器连接。

(3)可定义一寄存器s0\ s1 \ m0 \ m1\ h0 \ h1用于存放6个计数器的输出,分别存放百分之一秒、十分之一秒、秒、十秒、分、十分。由频率信号输出端输出频率为100HZ的时钟信号,输入到百分之一秒模块的时钟端clk,百分之一秒模块为100进制的计数器,当计数到“1001”时,百分之一秒模块清零,同时十分之一秒模块加1;十分之一秒模块也为100进制的计数器,当计数到“1001”时,十分之一秒模块清零,同时秒模块加1;以此类推。直到分模块计数到59进59。

(4)定义18位寄存器count用于存放分频和扫描用的计数值。27MHZ的时钟信号270000分频,得到100HZ的时钟信号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章