资料下载

×

如何使用FPGA实现贪吃蛇游戏的设计

消耗积分:0 |

格式:rar |

大小:0.60 MB |

2020-12-22

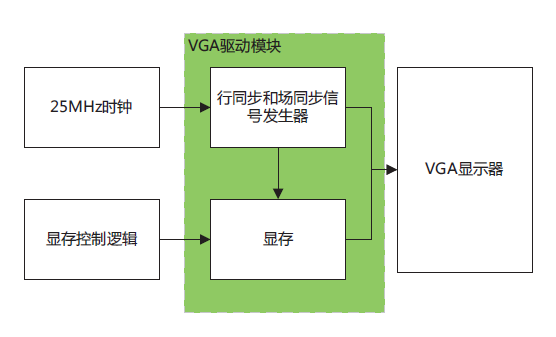

所以基本的设计思路就是通过计数器进行分频,按上述要求分别在行同步区或场同步区输出低电平,其它时刻为高电平,分别作为行同步信号和场同步信号。同时用计数器记录当前应该输出像素点的坐标值,从而能够从内存中读取相应像素值作为输出。在编程过程中由于 verilog语言中的赋值语句是并行执行的,因此无法判断其赋值完成的先后顺序,所以需注意逻辑关系,使在赋值后能够得到正确的判断结果。其中,显存模块是为贪吃蛇设计专门设计的模块。设计中将屏幕(640,480)分为(2015的点阵,每个小方格为边长32像素的小方格。这样划分的原因是32是2的幂次,从显存中选择输出像素时只需要简单地取地址高5位即可,从而简化了逻辑。显存大小为300bit,仅仅保存该点是否有“元素”(蛇身或豆子),至于是蛇身还是豆子,可以通过记录的豆子位置来判断。事实上,另外一种比较简单的实现办法是将显存改为600b,用0/1/2三种状态来判断没有元素/蛇身豆子,但是这样的操作浪费了一倍的资源,同时在判断是否吃到豆子时并没有能够简化逻辑,因此不是一个很好的解决方案。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章