资料下载

×

LVDS在FPGA中的使用教程之板级调试的详细概述

消耗积分:0 |

格式:rar |

大小:0.44 MB |

2020-12-30

趁着周末,写上一篇lvds调试文章,接着之前写的lvds连载系列,说说近期调试中遇到的一些问题。

电路板加工焊接回来后,先检查焊接、测试电源,FPGA程序下载及固化,各种调试。

好了,进入正是,说说lvds调试。如下图,采用软硬结合板设计,左侧为FPGA主板部分,右侧主要是一些接口,包括Camlink、VGA,中间采用柔性电路板相连。

首先,按照连载3的程序调试lvds接口,使用bank5的差分管脚输出lvds信号,结果采集卡采不到图,这下坏了,最开始怀疑引脚分配不正确,一番检查,问题不在这;

接着觉得走线可能不对,看了看PCB,5对差分信号,对内线长差控制在0.254mm内,对间线长差控制在2mm内,走线没有问题;

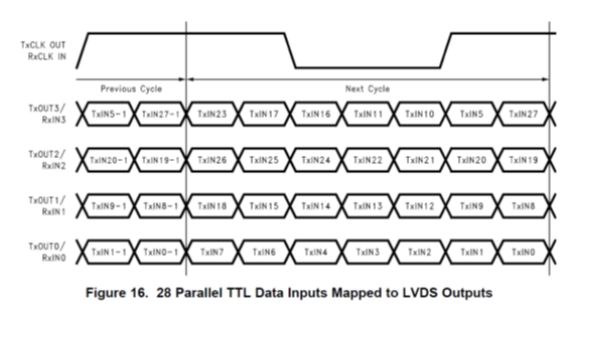

再接下来,怀疑Camlink位分配不正确,Camlink在base模式下包含11对差分线(4对数据,1对时钟,2对串口,4对相机控制),Camlink协议中有详细的位分配表,

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章