资料下载

Xilinx Kria KV260套件的第一个硬件项目

描述

警告:这不是一个完整的项目,而只是一个禁用风扇的简短技巧。

通过克隆 Vitis 平台存储库并为 Vivado 构建第一个平台,我了解到实际的风扇是由 KV260 上使用的 SOM 上使用的实际设备封装上的引脚 A12 驱动的。

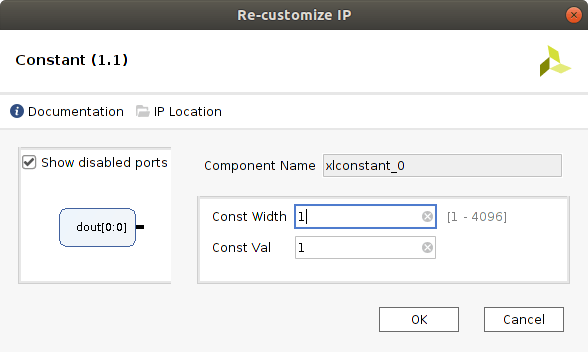

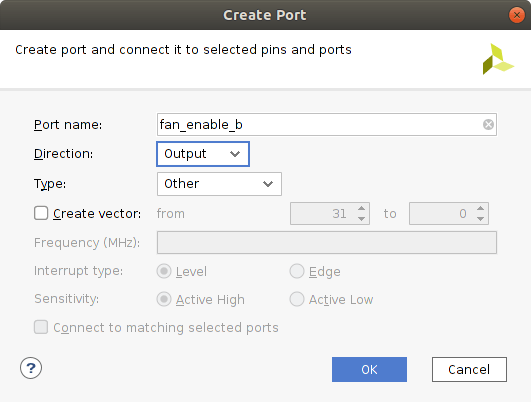

对于第一个项目,我只需将控制信号连接到逻辑“1”来关闭风扇。下一步当然将包括一个不错的温控风扇控制器,但首先我希望在不拉线的情况下停止烦人的声音。

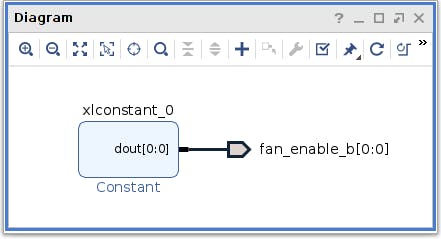

通过从常量到端口拉线来连接两个组件。

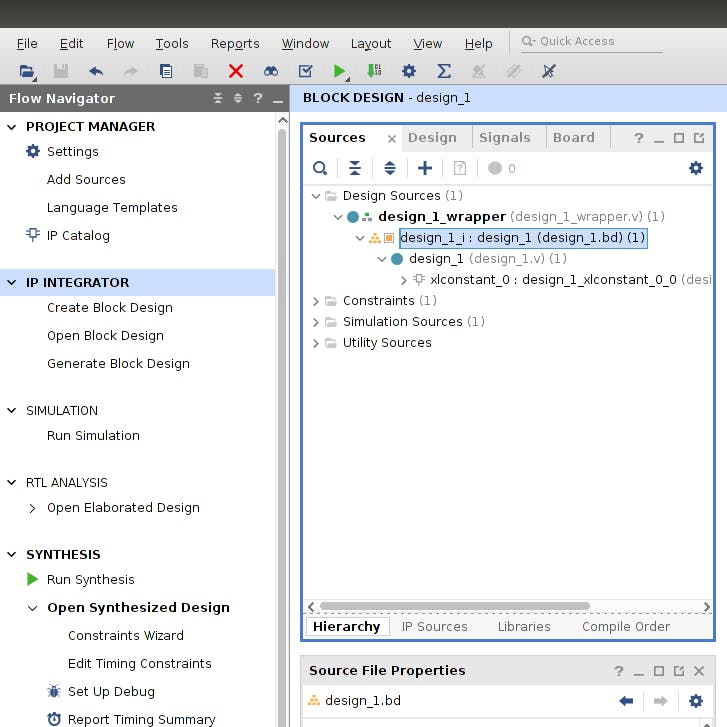

下一步是为 Block Design 创建一个 HDL 包装器。

通过右键单击设计源树中的 .bd 文件,您可以选择“创建 HDL Wrapper”并单击以简单地使用默认选择。

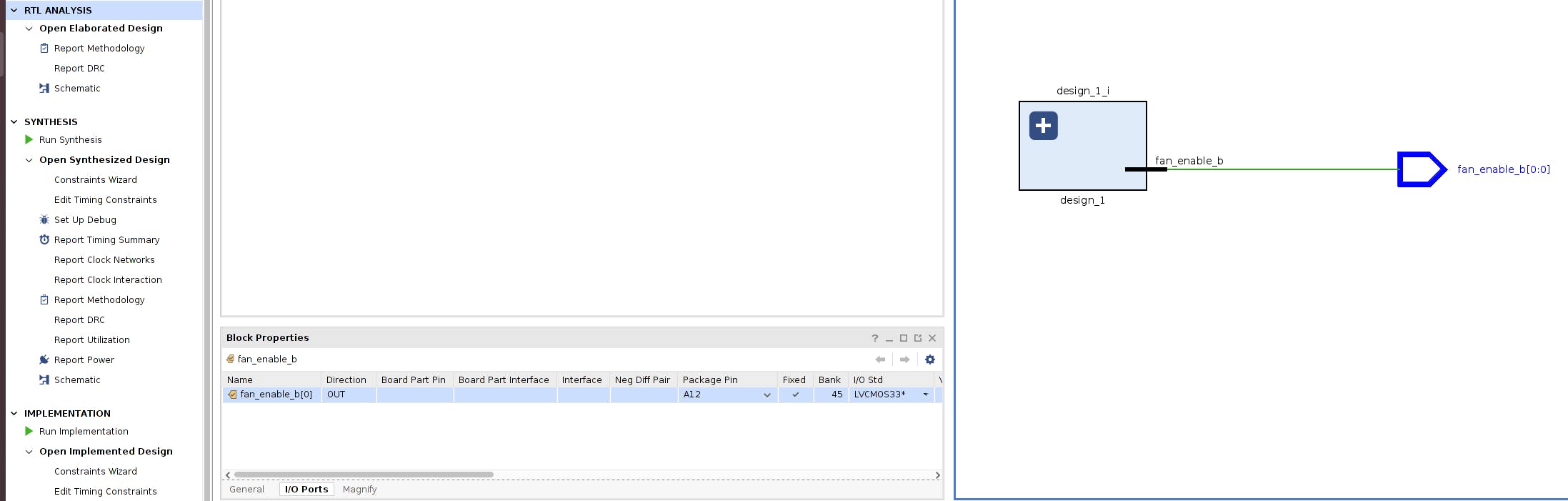

在 RTL 分析部分,您可以创建原理图,这是您可以将正确的封装引脚分配给创建的输出端口的众多要点之一。

将端口分配给封装引脚 A12 并选择 LVCMOS33 作为 I/O 标准。

现在您已准备好完全编译项目并生成比特流以在 Kria SOM 上配置 Zynq UltraScale+ 器件的 PL 部分。

只需从 Flow Navigator 的 Program and Debug 部分单击“Generate Bitstream”,Vivado 就会执行到达该点所需的所有步骤。这涉及到各种设计规则检查、综合和实际实现。我不会在这里详细介绍,

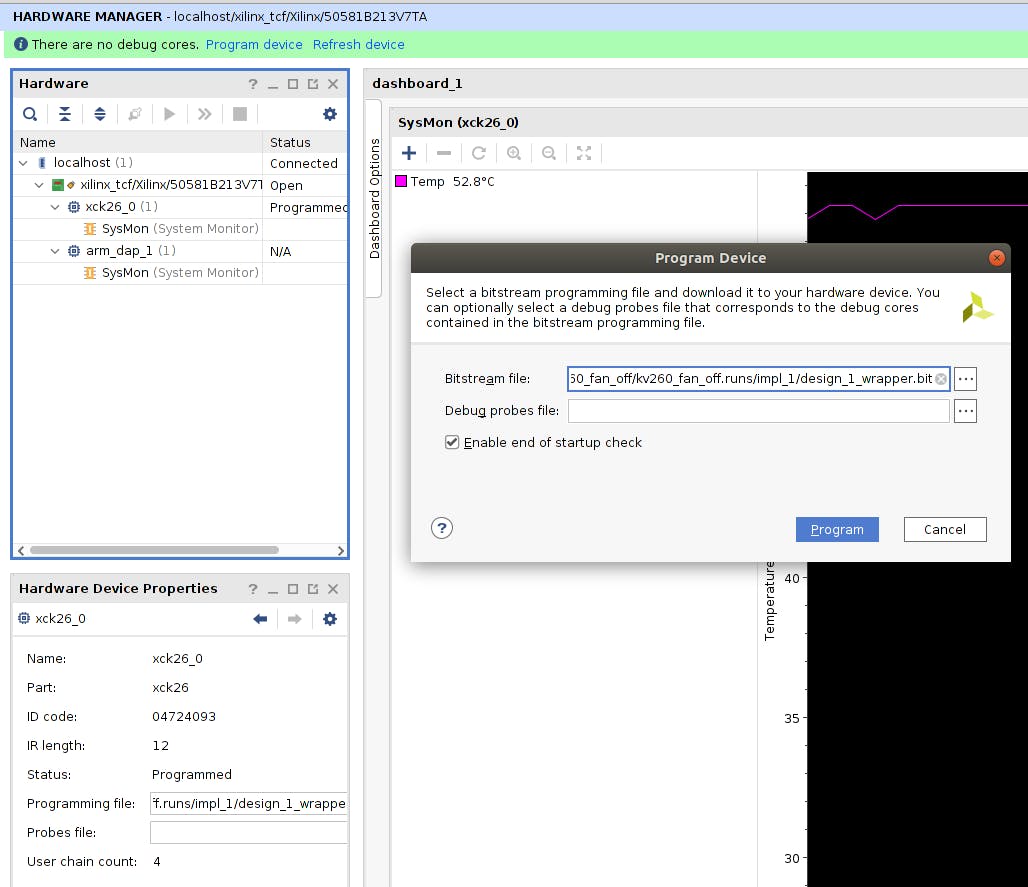

使用 microUSB 电缆和连接器 J4 将电路板连接到您的 PC 后,您应该能够连接到设备并使用比特流重新编程 xck26_0 设备。这将破坏在 PL 部分运行的加速应用程序,但风扇将停止运行,并且使用硬件管理器的 SysMon,您可以看到设备的温度开始攀升。我的温度稳定在 54 摄氏度,这对于记录但使用 JTAG 接口报告芯片温度的设备来说应该没问题。当然,这在实际项目中不可用,您应该始终实施控制方案,以便在温度开始上升到所需值以上(或接近数据表中指定的最高温度)时立即启动风扇。

就像上面的警告中所述,这只是一个快速而肮脏的黑客攻击,您可以利用获得的知识为 KV260 启动适当的热控制回路设计。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章