资料下载

DSP+ZYNQ双核通信案例开发手册

导读

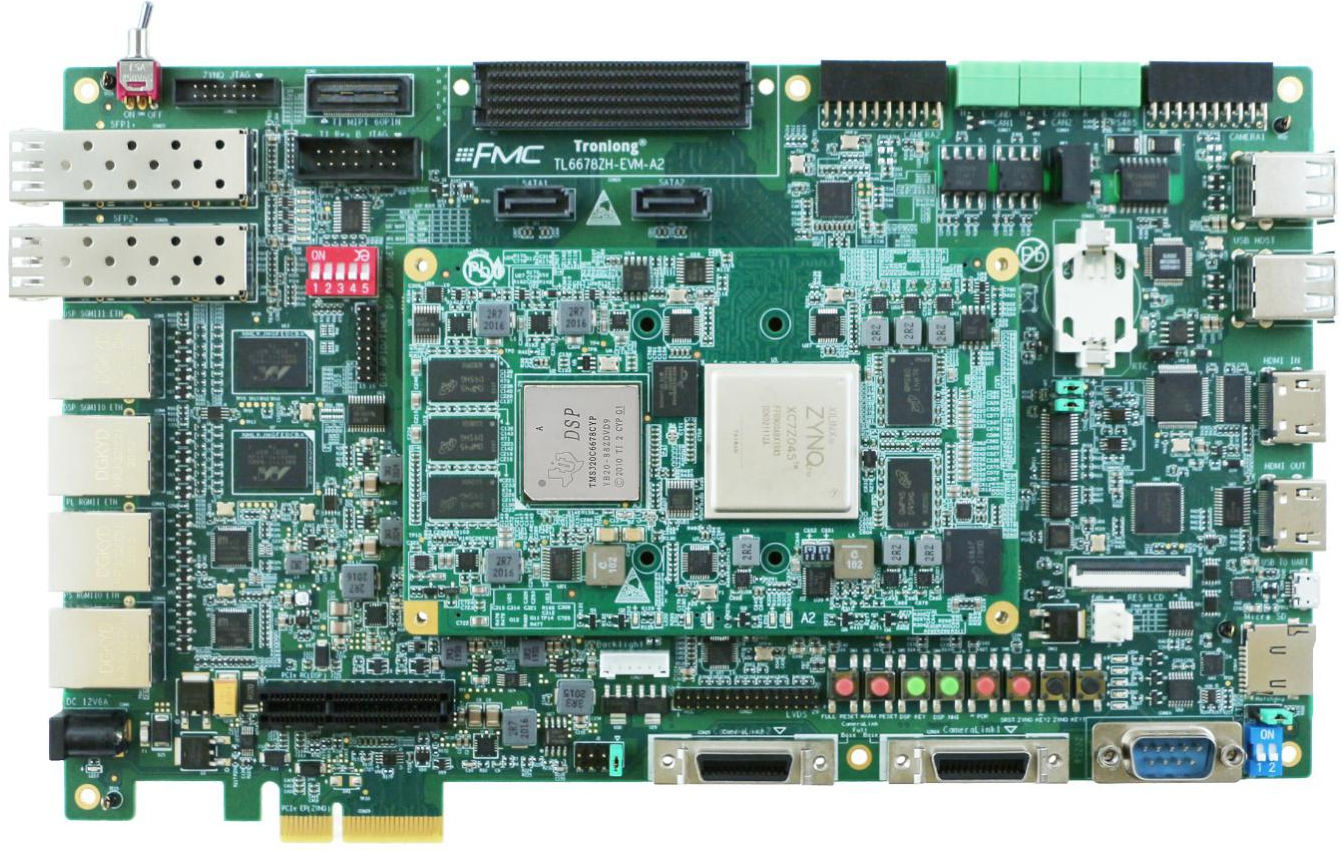

创龙科技TL6678ZH-EVM是一款基于TI KeyStone架构C6000系列TMS320C6678八核C66x定点/浮点DSP,以及Xilinx Zynq-7000系列XC7Z045/XC7Z100 SoC处理器设计的高端异构多核评估板,由核心板与底板组成。TMS320C6678每核心主频可高达1.25GHz,XC7Z045/XC7Z100集成PS端双核ARM Cortex-A9 + PL端Kintex-7架构28nm可编程逻辑资源。核心板内部DSP与ZYNQ通过SRIO通信总线连接。核心板经过专业的PCB Layout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

评估板接口资源丰富,引出双路CameraLink、双路SFP+光口、四路千兆网口、双路SATA、双路PCIe、四路USB、双路CAN、双路CAMERA、HDMI IN/OUT、LVDS、LCD、RS485、RS232、Micro SD、HPC FMC等接口,方便用户快速进行产品方案评估与技术预研。

创龙科技TL6678ZH-EVM评估板

目 录

前 言 ————4

1 I2C通信案例———— 5

1.1 案例说明———— 5

1.2 案例测试———— 5

1.3 关键代码———— 6

1.3.1 DSP工程———— 6

1.3.2 ZYNQ工程———— 7

2 SRIO通信案例———— 8

2.1 案例说明———— 9

2.2 案例测试———— 9

2.3 关键代码———— 9

2.3.1 DSP工程———— 9

2.3.2 ZYNQ工程———— 14

2.4 SRIO简介———— 19

2.5 模块/IP核配置 ————22

2.5.1 Serial RapidIO Gen2 IP核———— 22

2.5.2 srio_response_gen模块———— 24

2.6 申请IP核License———— 30

3 SRIO_AD9613案例———— 31

3.1 案例说明———— 31

3.2 案例测试———— 31

3.3 关键代码———— 40

3.3.1 DSP工程———— 40

3.3.2 ZYNQ工程 ————44

3.4 模块/IP核配置———— 46

3.4.1 SelectIO IP核———— 46

3.4.2 Serial RapidIO Gen2 IP核———— 49

3.4.3 data_to_srio模块———— 51

3.5 IP核License申请———— 58

4 SRIO_CameraLink案例———— 59

4.1 案例说明———— 59

4.2 案例测试———— 61

4.3 关键代码———— 64

4.3.1 DSP工程———— 64

4.3.2 ZYNQ工程———— 72

4.4 模块/IP核配置———— 74

4.4.1 Serial RapidIO Gen2 IP核———— 74

4.4.2 data_to_srio模块———— 76

4.4.3 lvds_n_x_1to7_sdr_rx模块———— 84

4.4.4 cameralink_bit_allocation_rx模块———— 85

4.5 综合案例编译———— 88

4.5.1 Vivado工程IP核License申请———— 88

4.5.2 JPEGEncode算法库安装———— 89

4.5.3 DSP端CCS工程macros.ini文件配置———— 94

5 flash_dsp案例———— 96

5.1 案例功能———— 96

5.2 操作说明———— 96

5.3 Vivado工程说明———— 100

5.3.1 ZYNQ7 Processing System IP核配置———— 100

5.3.2 引脚约束文件———— 101

更多帮助———— 103

资料简介

本文主要介绍基于SRIO和I2C接口的DSP + ZYNQ通信案例,适用开发环境:Windows 7/10 64bit、CCS 5.5.0、Xilinx Vivado 2017.4。案例分为DSP端程序和ZYNQ(PL)端程序两部分。

本文档案例程序默认使用DSP主频为1GHz的核心板,通过TL-XDS200仿真器和TL-DLC10下载器加载运行进行操作效果演示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章