资料下载

中文标准时钟系统

USC

标准时钟系统 (UCS)

UCS介 绍: 标准时钟系统模块支持低系统消耗和超低功耗。采用三种内部时钟信号,用户可以选择合适的性能和低功耗。标准时钟系统模块能够在软件控制下只需接一个或两个外部晶体,或振荡器下被配置操作。

UCS时钟源: 标准时钟系统模块包括多达五个时钟源。

·XT1CLK: 低频/高频振荡器,在XTS=0时,XT1处于低频(LF)模式,提

供一个32768HZ的低频时钟;在XTS=1时,XT1处于高频(HF)模式,可提供4M—32MHZ时钟频率。

·VLOCLK: 低功耗低频率振荡器,在对时间精确度要求不高的情况下提供12KHZ的时钟频率。

·REFOCLK: 内部参考低频振荡器,具有32768HZ典型频率,能够被用于作为FLL(锁频环)的参考时钟。

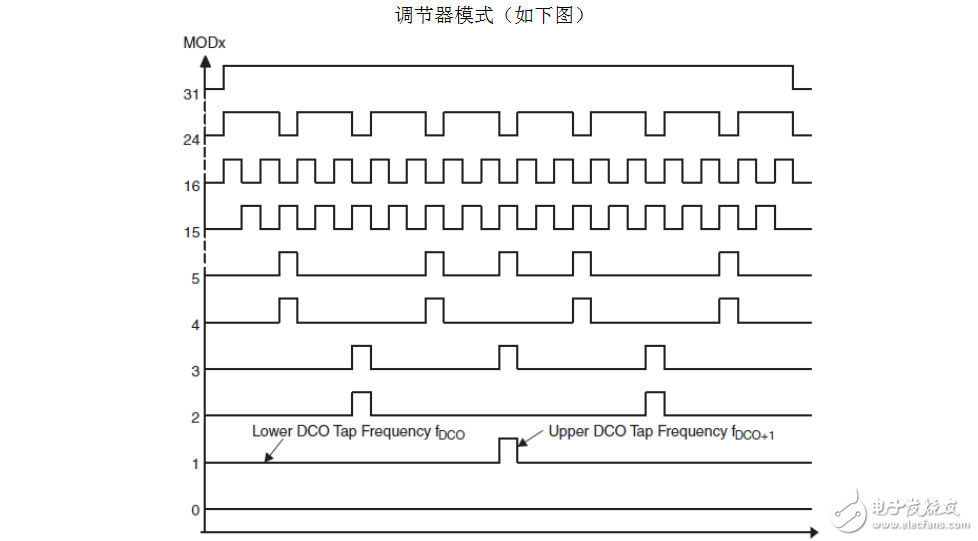

·DCOCLK: 内部数字控制振荡器,通过FLL来稳定其频率。

·XT2CLK: 可选择高频振荡器,同XT1 HF模式,可提供4M—32MHZ时钟频率。

UCS时钟信号:标准时钟系统模块具有三个内部时钟信号。

·ACLK: 可以通过软件选择XT1CLK、REFOCLK、VLOCLK、DCOCLK、XT2CLK(如被选择)作为其时钟源。(供外围模块使用)

·MCLK: 可以通过软件选择XT1CLK、REFOCLK、VLOCLK、DCOCLK、XT2CLK(如被选择)作为其时钟源。(供CPU和系统使用)

·SMCLK: 可以通过软件选择XT1CLK、REFOCLK、VLOCLK、DCOCLK、XT2CLK(如被选择)作为其时钟源。(供外围模块使用)

UCS默认配置:在PUC后,标准时钟系统模块的默认配置如下。

·XT1CLK为低频模式且作为ACLK的时钟源;

·MCLK和SMCLK选择DCOCLKDIV作为时钟源;

·FLL操作模式被使能,选择XT1CLK作为FLL参考时钟源,即FLLREFCLK;

·XIN/XOUT引脚被设置为通用I/O端口。XT1保持禁止,直到I/O端口被设置为XT1操作模式才使能XT1;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章