资料下载

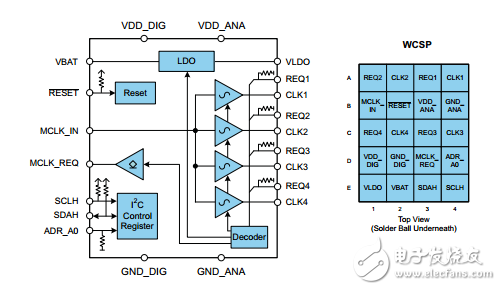

cdc3s04四正弦波时钟缓冲器与LDO

The CDC3S04 is a four-channel low-power low-jittersine-wave clock buffer. It can be used to buffer a single master clock to multiple peripherals. The foursine-wave outputs (CLK1–CLK4) are designed forminimal channel-to-channel skew and ultralow additive output jitter.

Each output has its own clock request inputs whichenables the dedicated clock output. These clockrequests are active-high (can also be changed to be active-low via I 2C), and an output signal is generated that can be sent back to the master clock to request the clock (MCLK_REQ)。 MCKL_REQ is an open-source output and supports the wired-OR function(default mode)。 It needs an external pulldown resistorMCKL_REQ can be changed to wired-AND or push- pull functionality via I 2C

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章