资料下载

×

高性能CPU的时钟网络设计

消耗积分:0 |

格式:rar |

大小:0.40 MB |

2017-10-30

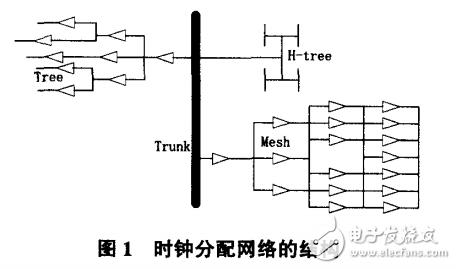

在同步数字系统中,时钟分配网络的设计直接影响系统的性能。在逻辑设计阶段,通常将时钟信号作为简单的同步控制信号加以处理,很少涉及时钟信号的物理特性。在实际的数字系统物理设计实现中,时钟分配网络的设计规划、时钟信号的具体布局、布线方式直接影响系统的性能和可靠性,并直接决定了芯片/系统的功耗。 在数字系统中,时钟信号具有下述特征:负载大,连线距离长,信号的翻转率高。由于时钟信号通常用来同步或者控制芯片/系统中的各个设计部分的具体操作,设计实现时要求时钟信号的波形具有很高的质量,即必须干净和陡峭,时钟信号的翻转时间短。此外,物理设计中对时钟信号延迟的控制必须特别小L“

,因为时钟信号延迟误差会直接导致数据穿透、数据失效的发生。 本文讨论物理设计中时钟分配网络的设计技术,并以高性能 CPU的时钟网络的设计为例,介绍了高性能CPU的时钟网络设计技

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章