资料下载

×

基于SHA-1算法的硬件设计及实现(FPGA实现)

消耗积分:0 |

格式:rar |

大小:0.81 MB |

2017-10-30

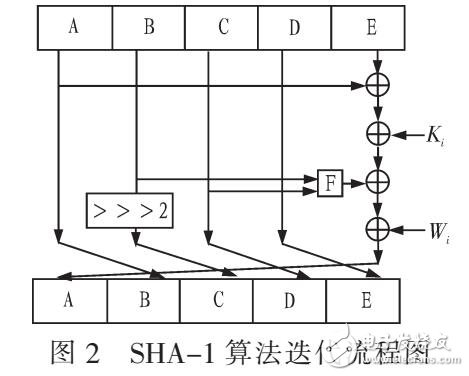

SHA-1(Secure Hash Algorithm)是一种非常流行的安全散列算法,为了满足各种应用对SHA-1算法计算速度的需要,该文围绕Hash 函数,基于本课题组的密文取情平台,对SHA-1算法进行深入研究,面向Xilinx K7 410T FPGA 芯片设计SHA-1算法实现结构,完成SHA-1算法编程,进行测试和后续应用。该算法在FPGA 上实现,可以实现3.2G bit/s的吞吐率,最大时钟频率为95 MHZ。仿真结果表明,与其它硬件设计相比,该算法在不影响原算法的安全的基础上可以获得更高的运行速度和吞吐量。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章

下载排行榜

- 暂无相关数据