资料下载

×

基于RS译码器设计和仿真

消耗积分:0 |

格式:rar |

大小:1.36 MB |

2017-11-07

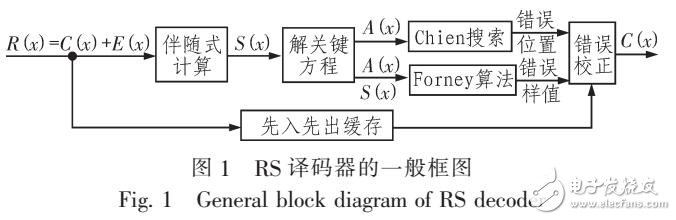

为了解决在RS译码中存在的译码过程复杂、译码速度慢和专用译码器价格高等问题,以RS(255,239)码为例,采用了基于改进的无求逆运算的Berlekamp-Massey( BM)迭代算法。结合FP(;A平台,利用Xilinx lSE软件和Verilog硬件描述语言,对译码器中各个子模块进行了设计和仿真。整个译码器设计过程采用流水线处理方式。时序仿真结果表明在保证错误符号不大于8个的情况下,经过295个固有延迟之后,每个时钟周期均可连续输出经校正的码字,该RS译码器的纠错能力能够达到预期要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章