资料下载

×

基于AES算法研究与设计

消耗积分:0 |

格式:rar |

大小:1.00 MB |

2017-12-03

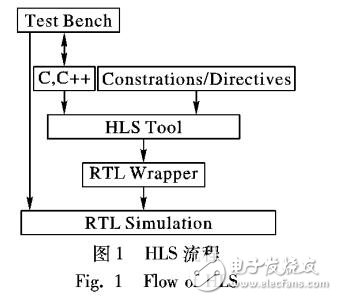

由于对广泛使用的AES算法的性能要求越来越高,基于软件的密码算法已经越来越难以满足高吞吐量密码破解的需求,因此越来越多的算法利用现场可编程逻辑门阵列( FPGA)平台进行加速。针对AES算法在FPCA硬件上存在的开发复杂度高且开发周期长等问题,采用高层次综合( HLS)设计方法,使用高级程序语言描述并设计AES硬件加速算法。首先利用循环展开等提高运算并行度;其次使用资源平衡技术进行优化,充分利用片上存储和电路资源;最后添加全流水结构,提高整体设计的时钟频率和吞吐量,同时也详细对比分析基准设计、利用结构展开、资源均衡以及流水线优化方法的设计。经过实验表明,在Xilinx xc72020clg484 FPCA芯片上,最终AES算法的时钟频率最高达到127. 06 MHz,而吞吐量达到了16. 26 Cb/s,较之基准的AES设计,性能提升了三个数量级。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章

下载排行榜

- 暂无相关数据