资料下载

×

基于FPGA的安检机图像数据排序算法实现

消耗积分:1 |

格式:rar |

大小:4.14 MB |

2018-04-26

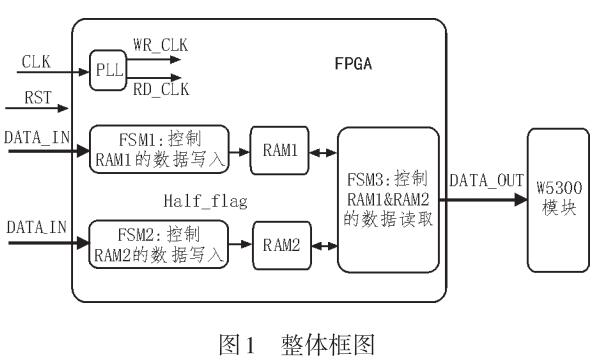

在传统的安检机数据采集传输系统中,控制芯片直接将AD采集的前端X射线探测器的数据传输到上位机中,然后上位机软件冉对数据进行排序整理然后再进行图像数据的处理,这样不仅对上位机CPU增加了处理负担,而且降低了图像数据的处理速度,大大降低了安检机的安检效率;本设计利用FPGA的高速数据处理特性,通过对AD采集的前端双能X射线探测器的图像数据在双端口RAM中进行排序处理,然后通过以太网将排序好的图像数据传输到上位机中,这样不仅降低了上位机CPU的占用率而且提高了上位机图像处理的速度,使安检机的实时性能得到更好的提高。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章

下载排行榜

- 暂无相关数据