资料下载

×

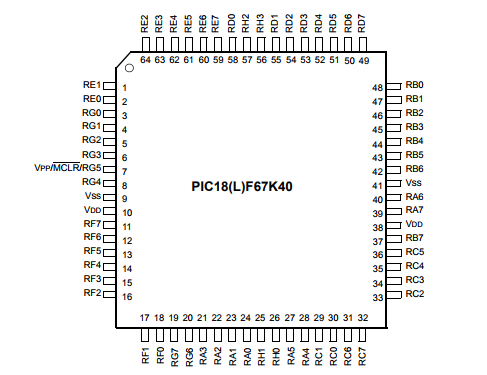

基于PIC18(L)F67K40的采用 XLP 技术的 64 引脚低功耗高性能单片机

消耗积分:5 |

格式:pdf |

大小:10.57 MB |

2018-05-25

内核特性

• C 编译器优化的 RISC 架构

• 仅 83 条指令

• 工作速度:

- DC – 64 MHz 时钟输入

- 最小指令周期为 62.5 ns

• 可编程 2 级中断优先级

• 31 级深硬件堆栈

• 4 个带硬件限制定时器 (Hardware Limit Timer,

HLT)的 8 位定时器 (TMR2/4/6/8)

• 5 个 16 位定时器 (TMR0/1/3/5/7)

• 低电流上电复位 (Power-on Reset, POR)

• 上电延时定时器 (Power-up Timer, PWRT)

• 欠压复位 (Brown-out Reset, BOR)

• 低功耗 BOR (LPBOR)选项

• 可编程代码保护

• 窗口看门狗定时器 (WWDT):

- 定时器监视上溢和下溢事件

- 可变预分频比选择

- 可变窗口大小选择

- 可在硬件或软件中配置所有源

存储器

• 128 KB 闪存程序存储器

• 3568 字节的数据 SRAM 存储器

• 1024 字节的数据 EEPROM

• 直接、间接和相对寻址模式

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章