资料下载

×

基于EVAL-ADF4351EB1Z时钟合成器的参考设计

消耗积分:2 |

格式:pdf |

大小:73.35KB |

2021-01-14

说明

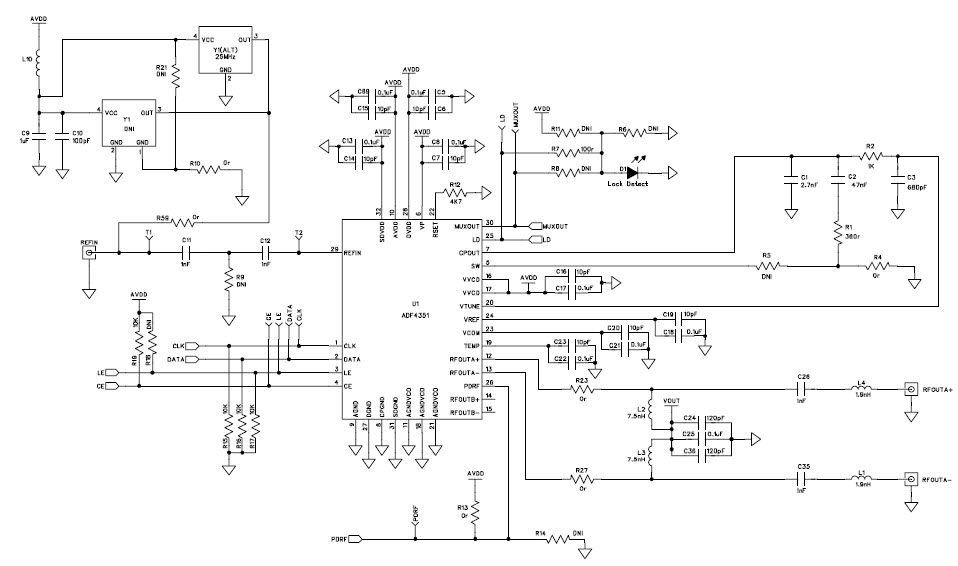

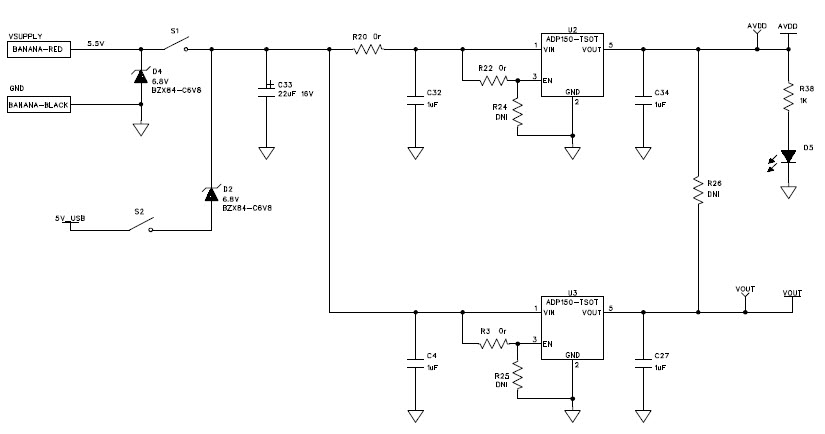

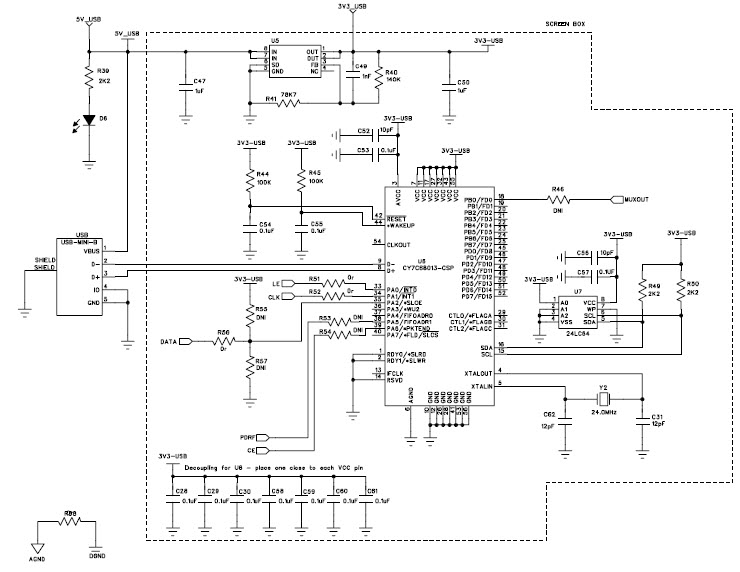

- EVAL-ADF4351EB1Z,此板用于允许用户评估锁相环(PLL)的ADF4351频率合成器的性能。它显示了该板,其中包含集成的ADF4351合成器和VCO,用于输出信号的SMA连接器,电源,基准振荡器和USB连接器。板上还有一个环路滤波器(35 kHz)。评估板设置为 25 MHz PFD比较频率。板载TCXO提供 25 MHz 参考频率

主要特色

-

工作频率25 MHz

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章