资料下载

FPGA Express VHDL的参考手册免费下载

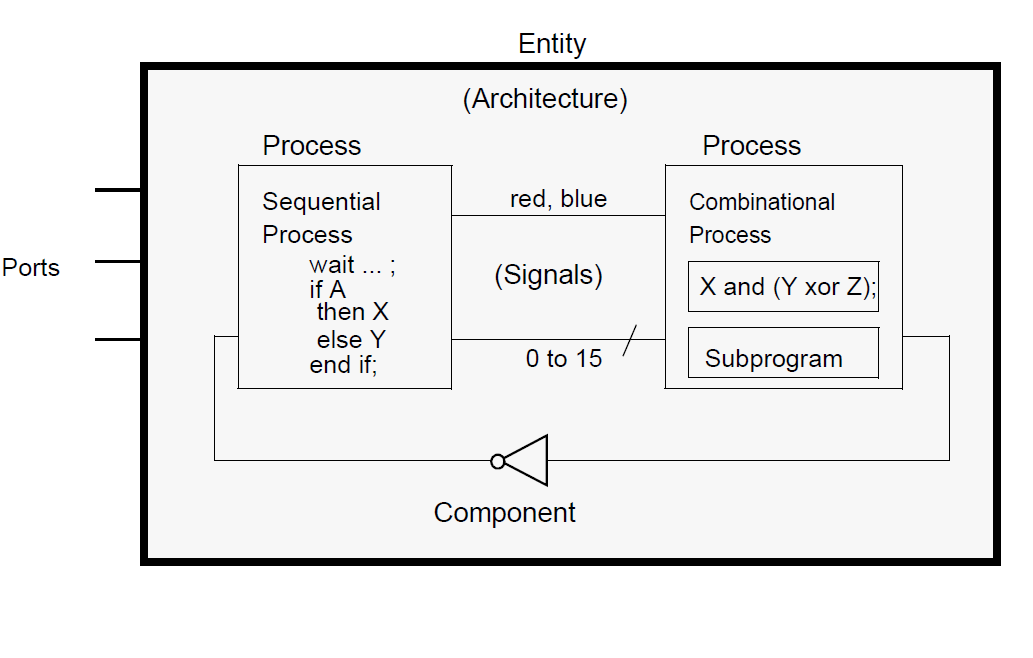

FPGA Express将VHDL描述转换并优化为内部门级等效格式。然后针对给定的FPGA技术编译此格式。

要使用VHDL,请熟悉以下概念:

•硬件描述语言

•关于VHDL

•关于FPGA Express

•使用FPGA Express

•设计过程模型

美国国防部,作为其超高速集成电路(VHSIC)计划的一部分,于1982年开发了VHSIC HDL(VHDL)。VHDL描述了数字电路设计的行为、功能、输入和输出。VHDL在风格和语法上与现代编程语言相似,但包含许多特定于硬件的结构。

FPGA Express读取并解析支持的VHDL语法。第11章,“HDL构造”列出了所有VHDL构造,并包括为每个构造提供的synopsys支持级别。

硬件描述语言(HDL)用来描述离散电子系统的结构和行为系统.HDLs是为了应对日益复杂的设计而开发的。从机器代码(晶体管和焊料),到汇编语言(网表),再到高级语言(HDL),软件描述语言的发展常常有相似之处

自上而下,基于HDL的系统设计在大型项目中最有用,在大型项目中,有几个设计师或设计师团队在工作高密度脂蛋白提供结构化开发。在做出了主要的体系结构决策,并且确定了主要组件及其连接之后,可以独立地进行子项目的工作。

HDL通常支持混合级别的描述,其中结构或网表构造可以与行为或算法混合描述。使用这种混合级别的功能,可以在高抽象级别上描述系统架构;然后逐步将设计细化为特定的组件级或门级实现。或者,您可以将HDL设计描述读入FPGA Express,然后指导编译器自动合成门级实现。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章