资料下载

RF系统设计基准输入电路和分配器

引言

要为RF系统设计基准输入电路证明是棘手的事情。难题之一是在满足时钟的保护、缓冲及分配要求的同时也要保持输入时钟的相位噪声性能。本文将说明怎样设计一款10MHz基准输入电路并优化其性能。

设计要求

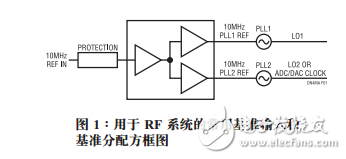

RF 仪器和无线收发器常常具有一个用于外部基准时钟的输入,例如:RF 仪器上广泛使用的 10MHz 基准输入端口。许多同类系统都包括一种装置以用于在整个系统中分配基准时钟。图 1 示出了一款常用方案,其中由基准时钟向两个不同的锁相环 (PLL) 提供基准输入。

设计精良的坚固型输入可接受宽幅度范围的正弦波和方波信号。即使在输入多变的情况下,其也可保持向系统内部的目标PLL输入提供恒定的信号电平驱动。完全暴露的基准输入端口应当具备过压 / 过功率保护功能。最重要的是:对于不可避免的时钟信号相位噪声性能下降,应最大限度地加以抑制。

设计实现方案

LTC®6957 是一款非常低附加噪声 (或抖动) 的双输出时钟缓冲器和逻辑转换器。LTC6957 的输入可接受宽幅度范围的正弦波或方波信号,并以恒定的幅度驱动负载。

LTC6957 提供了各种不同的输出逻辑信号选项: PECL、LVDS 和 CMOS (同相及互补型),从而使其能驱动多种负载。图 2 示出了一款采用 LTC6957-3 的 10MHz 基准输入电路,其可产生两个同相 CMOS 输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章