资料下载

×

基于FPGA和DSP的高速图像处理系统

消耗积分:0 |

格式:rar |

大小:0.44 MB |

2017-10-19

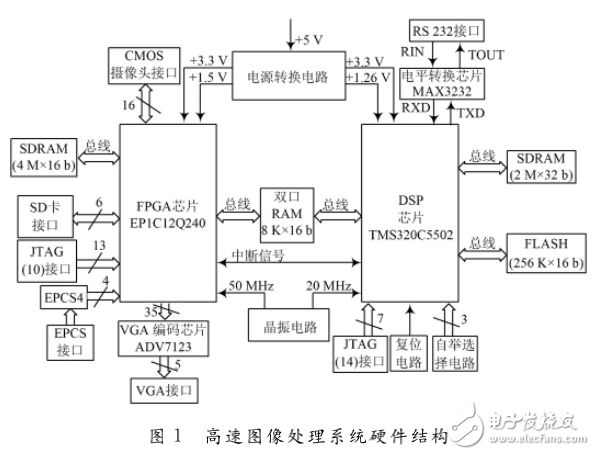

图像处理系统主要由 CMOS图像传感器(MT9M011)、

FPGA(EP1C12Q240C8)、双 口 RAM(CY7C025)、DSP(TM320VC5502)、视频 D/A(ADV7123)和一些存储器

等组成[3-4],如 图1所 示。首 先,在图像采集模块控制

COMS图像传感器 下,图 像 数 据 则 以25f/s的 速 率 向

FPGA 输送。然 后,通 过 FPGA 的 控 制 使 其 缓 存 在 片

外的SDRAM 中,之后实时显示模块控制 ADV7123做

到了对图像的实时显示。如果用户通过外部控制,选择

了压缩模式,则原始的图像数据将由帧存模块移至高速

缓冲模块中,DSP通过 EMIF接口外扩存储器的方式,

高效的读取双口 RAM 中的图像数据。最后,图像数据

在 DSP内部做好JPEG 压缩后,以相同 的 方 式 通 过 高

速缓冲模块,把数据传给 FPGA 的存储控制模块,做到

压缩图像数据的存储。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章