资料下载

×

基于AES算法硬件优化及IP核应用

消耗积分:1 |

格式:rar |

大小:0.90 MB |

2017-11-02

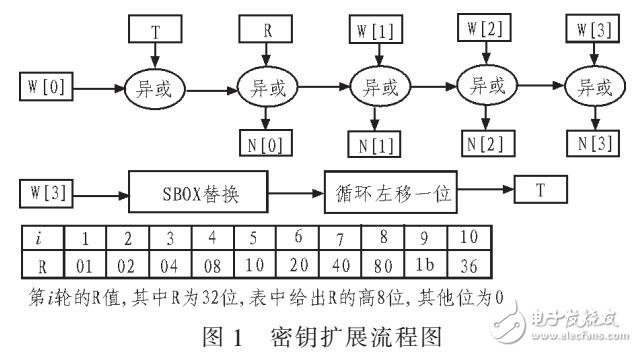

根据AES算法的特点,从3方面对算法硬件实现进行改进:列混合部分使用查找表代替矩阵变换,降低算法实现的运算复杂度,采用流水线结构优化关键路径一密钥拓展,提升加密速度,利用FPGA定制RAM (BRAM)预存查找表进一步提升加密速度。优化后的AES算法在Virtex -6xc6vlx240T(速度等级-3)FPGA上实现,结果发现,AES算法共占用1 139个Slice,最大频率达到443.99 MHz,通量达到56.83 Gbit/s,效率达到49.89 (Mbit/s)/Slice;然后,对AES算法进行接口逻辑声明,将优化后AES算法封装成自定制IP核;最后,采用基于NIOS II的SOPC技术,构建了一个嵌入式AES算法加密系统,实现了数据通信中的高速加密。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章

下载排行榜

- 暂无相关数据