资料下载

×

基于Matlab的并行循环冗余校验Verilog代码自动生成方法

消耗积分:3 |

格式:rar |

大小:0.97 MB |

2017-12-12

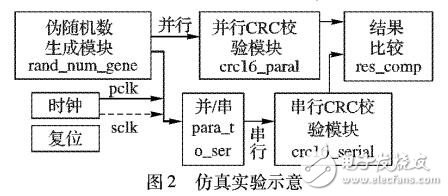

在水声信号探测数据的传输过程中,现场可编程门阵列( FPGA)通过传统串行方法对长数据帧进行循环冗余校验(CRC)时无法达到速度要求,而更快速的并行校验方法存在因编程复杂带来的实际工程应用困难问题。为了满足传输对校验速度的需求,降低编程难度和缩短编程时间,设计了一种借助Matlab对任意长度数据帧自动编写并行CRC程序语句的方法。该计算方法基于矩阵法数学原理,借助Matlab完成所有数学推导计算过程,然后直接输出符合Verilog HDL语法规则的并行CRC校验程序语句。通过在QuartusⅡ9.0中仿真,进一步在民用拖曳声呐阵列系统上进行数据传输实验,验证了Matlab自动编程方法的有效性:校验程序的自动编写输出能在几十秒内完成,同时生成的并行CRC校验程序能在满足数据传输速度要求的情况下正确地计算出系统中传输协议定义的长数据帧的校验码。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章