资料下载

×

浮点运算单元的FPGA实现

消耗积分:0 |

格式:rar |

大小:0.25 MB |

2018-04-10

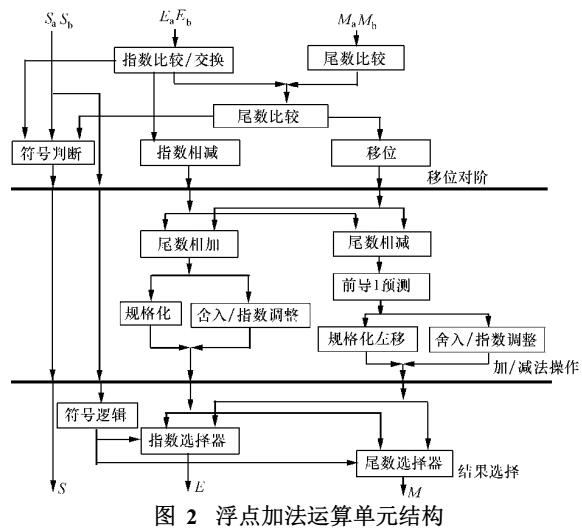

浮点加法是数字信号处理中的一种非常频繁且非常重要的操作,在现代数字信号处理应用中,浮点加法运算几乎占到全部浮点操作的一半以上。浮点乘法器是高性能DSP(数字信号处理器)的重要部件,是实时处理的核心,其速度直接影响DSP的速度,因此国内外学者对提高浮点乘加单元的性能进行了大量的研究。浮点运算单元的设计主要是在速度和所占用资源之间进行权衡。

本文以实时信号处理为应用背景,首先介绍了单精度浮点格式,然后从速度和占用资源这两个角度出发,详细介绍了浮点乘法单元和浮点加法单元的流水线结构。经过仿真验证,在V irte x-4系列FPGA(现场可编程门阵列)上,浮点加法器的最高运行速率达到405 MHz,而浮点乘法器的最高运行速率达到429 MHz。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章