资料下载

CPCI6U-2DSP-C6678信号处理板的说明书免费下载

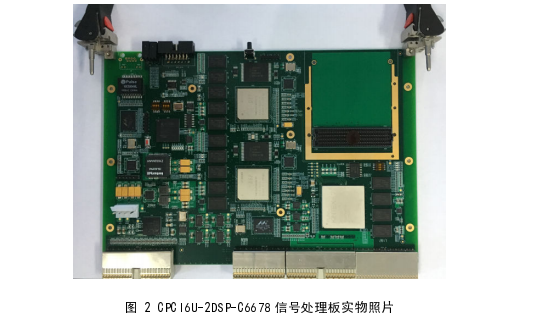

CPCI6U-2DSP-C6678 信号处理板(以下简称信号处理板)基于 6U CPCI 规范,并且具有一个基于 FMC 规范的 HPC 接口。信号处理板采用双 DSP+FPGA 的处理架构,DSP 采用 TI 公司最新一代 DSP TMS320C6678,FPGA 采用 XC7K325T-1FFG900I 芯片,设计采用工业级芯片。DSP 最高可支持 4GB 的 DDR3 SDRAM, FPGA 最高可支持 2GB 容量 DDR3 SDRAM,板间可以通过 CPCI、GTX、LVDS IO 和 FMC HPC 接口进行互联扩展。该板卡主要应用于雷达、电子对抗、软件无线电等领域。本文包括:处理板卡的基本原理、关键器件说明、各接口说明以及使用说明等。

功能和技术指标

处理能力:

2 片 TMS320C6678 8-CORES @1GHz/1.25GHz;

1 片 Kintex7 XC7K325T(可兼容 XC7K410T);

存储容量:

FPGA 上 2GB DDR3 SDRAM,1 组 64bits@1000Mbps;

每片 DSP 各 2GB DDR3 SDRAM,各 1 组 64bits@1333Mbps;

传输能力:

千兆以太网:前面板上 1 路、底板接插件 J5 上 1 路;

FMC HPC 接口:1 个,含 80 对 LVDS 差分线;

J1: 32bits/66MHz CPCI 总线;

J3:2 路 4x GTX,1 路 2x PCIe;

J4:24 对 LVDS@1Gbps;

J5:2 路 RS232,8 路 DAC 模拟信号,1 路千兆以太网。

工作温度范围:商业级 0~50℃;工业级 -40~60℃;

典型功耗:25W。

信号处理板主要由两片 8 核的主频为 1.25GHz 的 TMS320C6678(后简称 DSP)组成。两片 DSP 的外围电路采用相同的设计;每片 DSP 外接 32MB 的 16bits 位宽并口 NOR Flash 和 2GB 的 DDR3 SDRAM;两片 DSP 之间通过 1 路 Hyperlink 和 1 路 SGMII 接口互联;DSP2 实现 1 路千兆以太网接口并与 CPCI J5 接插件互联,用于板间扩展;两片 DSP 分别将 1 路 4x SRIO 与 MFPGA 互联。DSP2 的 PCIE 接口通过 PCI-PCIe 桥芯片转化为 32bits 位宽、66MHz 的 PCI 总线接口。DSP1 的的 PCIE 接口连接到了 CPCI J3 接 插 件 。 MFPGA 的 型 号 为 Xilinx XC7K325T-1FFG900I , 可 设 计 兼 容 更 高 性 能 的 XC7K410T-1FFG900I。FPGA 外挂 1 组 DDR3 SDRAM,接口宽度为 64bits,容量为 2GB。MFPGA 连接了个 4x 的 GTX 接口到 CPCI J3 接插件,用于板间扩展。每片 DSP 的 2 个 SPI 分别与 CFPGA 和 MFPGA 互联。

本板卡上有两片 FPGA 芯片,其中 MFPGA 是主要的接口和处理芯片,CFPGA 主要用板卡时钟网络配置、电源上电顺序控制以及接口转换作用。CFPGA 外接一片 8 通道 DAC 芯片,采样率不低于 50Ksps,精度为 16bits,8 路模拟信号通过 CPCI J5 输出给底板。 CFPGA 外挂 MAX3160 芯片,可通过 CPCI J5 实现两路 RS232 接口。CFPGA 分别通过 1 个 SPI 接口与 DSP 互联。MFPGA 外接同步、复位等信号至 CPCI J5,可实现外部设备对本板卡的同步触发等功能。MFPGA 外接 24 对 LVDS 信号至 CPCI J4,可实现数据传输等功能。本载板还具有一个通过 MFPGA 扩展的 FMC HPC 接口,可扣载 1 块 FMC 子板。信号处理板供电电压为+5V 和+3.3V,要求全部器件具有工业级产品,板卡工作温度满足-40℃~+60℃的要求。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章