资料下载

×

如何设计一种低静态电流高稳定性的低压差线性稳压器

消耗积分:0 |

格式:rar |

大小:11.30 MB |

2019-12-20

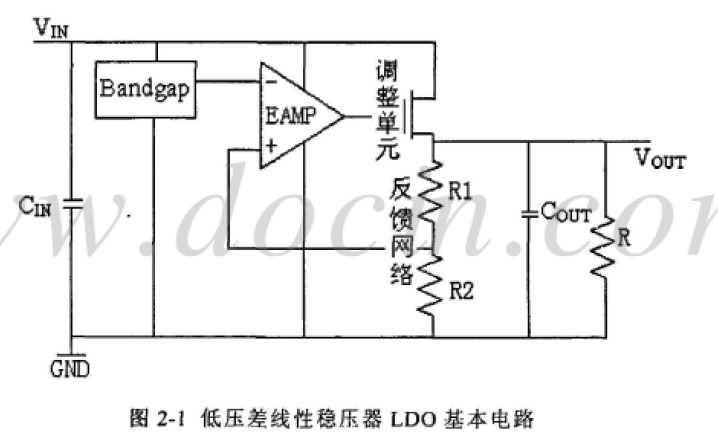

电源技术飞速发展的今天,高性能、低功耗、高稳定性电源管理方案成为各类便携式电子产品设计的必要考虑因素。本文根据低压差线性稳压器的工作原理,构建了LDO整体架构、并制定了芯片的各项设计指标,最终设计了一种低静态电流、高稳定性的低压差线性稳压器系统(主要模块包括带隙基准电压源、误差放大器、偏置电路以及使能电路等)。

设计采用CSMC公司0.5um CMOS工艺,使用铿腾公司的Composer与Virtuoso分别进行了电路与版图设计,并使用Spectre对电路进行仿真验证。仿真结果表明:系统正常工作电压为2.0V至5.0V(典型输入为3.3V),输出电压为1.8V至5.0V(典型输出为3.0V),输入输出压降为300mV,静态电流小于30uA。在温度范围40℃~+125℃内系统能保持良好的稳定性,达到了设计要求。此外,该LDO在芯片内部集成了过温保护电路、过流保护电路以及静电放电保护电路,因此能最大限度保护芯片稳定工作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章