资料下载

×

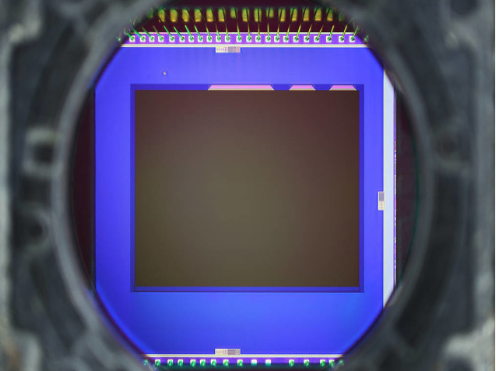

N阱CMOS工艺流程的详细资料说明

消耗积分:4 |

格式:ppt |

大小:1.72 MB |

2020-10-01

CMOS集成电路通常制造在尽可能重掺杂硼的P型(100)衬底上以减小衬底电阻 ,防止闩锁效应。

CMOS工艺的第一步是在衬底上生长一层轻掺杂的P型外延层,比标准双极工艺采用的外延层薄很多。理论上CMOS工艺不需要外延层,因为MOS管可以直接在P型衬底上形成。外延工艺增加了成本,但是采用P+衬底可以提高抗闩锁效应的能力。

P型外延场区接受P型的沟道终止注入,而N阱场区接受N型沟道终止注入,这里包含大面积硼注入和选择性磷注入

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章