资料下载

音频编解码器串行接口配置

摘要

音频串行接口(ASI)提供了一种在处理器之间传输非缓冲音频数据的方法和/或音频转换器。这些数据通常编码PCM二进制补码格式,虽然其他形式的变化,可以实现压缩的低数据率传输。音频基于∑-Δ转换器(ΔΣ)架构需要一个主时钟在运比目标采样速率快得多。虽然有几种方法来获得这个主人时钟,必须小心,以确保这个时钟不会漂移的ASI。本报告讨论了几种配置,防止这种情况。

介绍

每个系统有不同的要求,当涉及到接口的音频编解码器ASI。最常见的配置是主和从模式。当音频编解码器ASI配置在主模式,它的位时钟(BCLK)和字时钟(WCLK)输出引脚。在从模式下,总线时钟和对编解码器的ASI输入WCLK。这种关系看起来很简单。然而,必须小心当我被配置在主从模式确保摧毁过采样数据总是在正确的目标率时间槽。

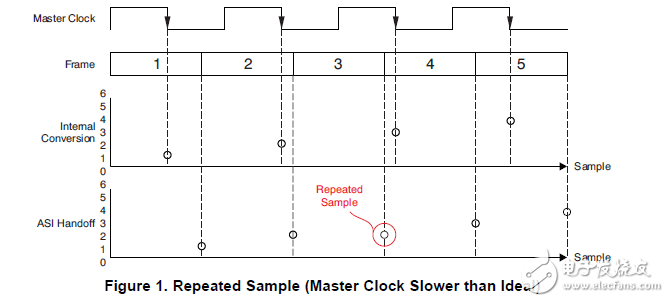

如果主时钟是一个自由运行的时钟,它被馈送到一个转换器,它不会被频率锁定到帧时钟(WCLK)一个独立的ASI。任何偏离理想最终会导致跳过或重复抽样(假设体系结构重复样本)。例如,如果主机处理器提供了一个理想的48 kHz的WCLK相对于绝对时间,其各自的理想主时钟可以正(128●WCLK)= 6.144 MHz。如果一个非理想晶体的主时钟直接提供给转换器调制器与0.001%的错误,这个时钟可能会导致6.14393856兆赫。最终这个慢时钟将导致重复采样的ASI总线。当然,没有理想这样的东西主或ASI时钟。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章