资料下载

×

PL与CPU通过DDR3进行数据交互的应用设计

消耗积分:0 |

格式:rar |

大小:0.1 MB |

2017-09-15

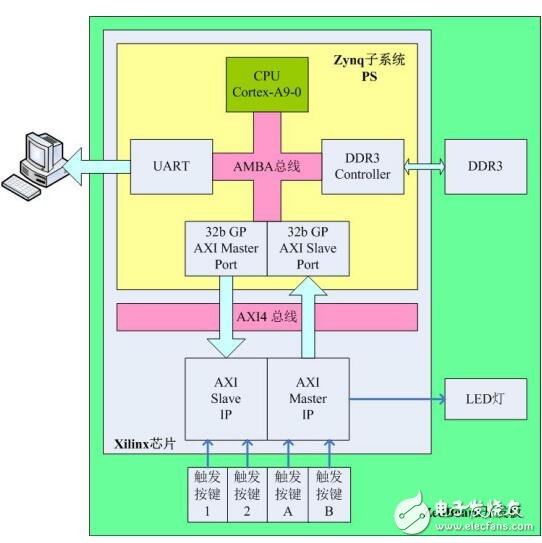

通过之前的学习,CPU可以读写DDR3了,PL端的Master IP也可以读写DDR3了,那二者就可以以DDR3为纽带,实现大批量数据交互传输。

这样的话,整个系统将会有两个master,即CPU和PL端的Master IP核,共同访问操作一个Slave端即DDR3 Controllor。

本次实验就是构建一个这样的验证系统。当然了在真正的工程系统中,还需要设计良好的读写同步,防止竞争冲突,这就属于系统设计层面的了,本实验依靠按钮触发有用户来进行读写同步。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章