资料下载

ad7266差分单端输入双路 2位、12位、三通道SAR ADC

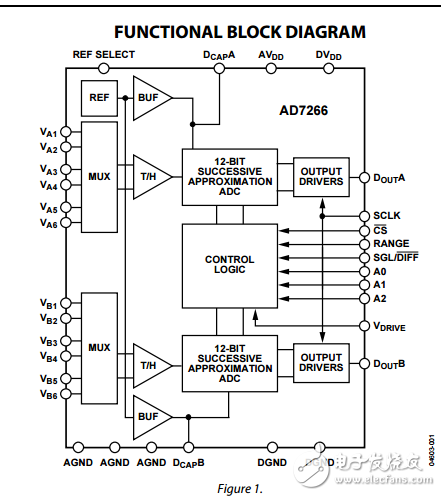

The AD72661 is a dual, 12-bit, high speed, low power, successive approximation ADC that operates from a single 2.7 V to 5.25 V power supply and features throughput rates up to 2 MSPS. The device contains two ADCs, each preceded by a 3-channel multiplexer, and a low noise, wide bandwidth track-and-hold amplifier that can handle input frequencies in excess of 30 MHz. The conversion process and data acquisition use standard control inputs allowing easy interfacing to microprocessors or DSPs. The input signal is sampled on the falling edge of CS; conversion is also initiated at this point. The conversion time is determined by the SCLK frequency. There are no pipelined delays associated with the part. The AD7266 uses advanced design techniques to achieve very low power dissipation at high throughput rates. With 5 V supplies and a 2 MSPS throughput rate, the part consumes 6.2 mA maximum. The part also offers flexible power/ throughput rate management when operating in normal mode as the quiescent current consumption is so low. The analog input range for the part can be selected to be a 0 V to VREF (or 2 × VREF) range, with either straight binary or twos complement output coding. The AD7266 has an on-chip 2.5 V reference that can be overdriven when an external reference is preferred. This external reference range is 100 mV to VDD.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章