资料下载

W25Q256FV串行闪存芯片的数据手册免费下载

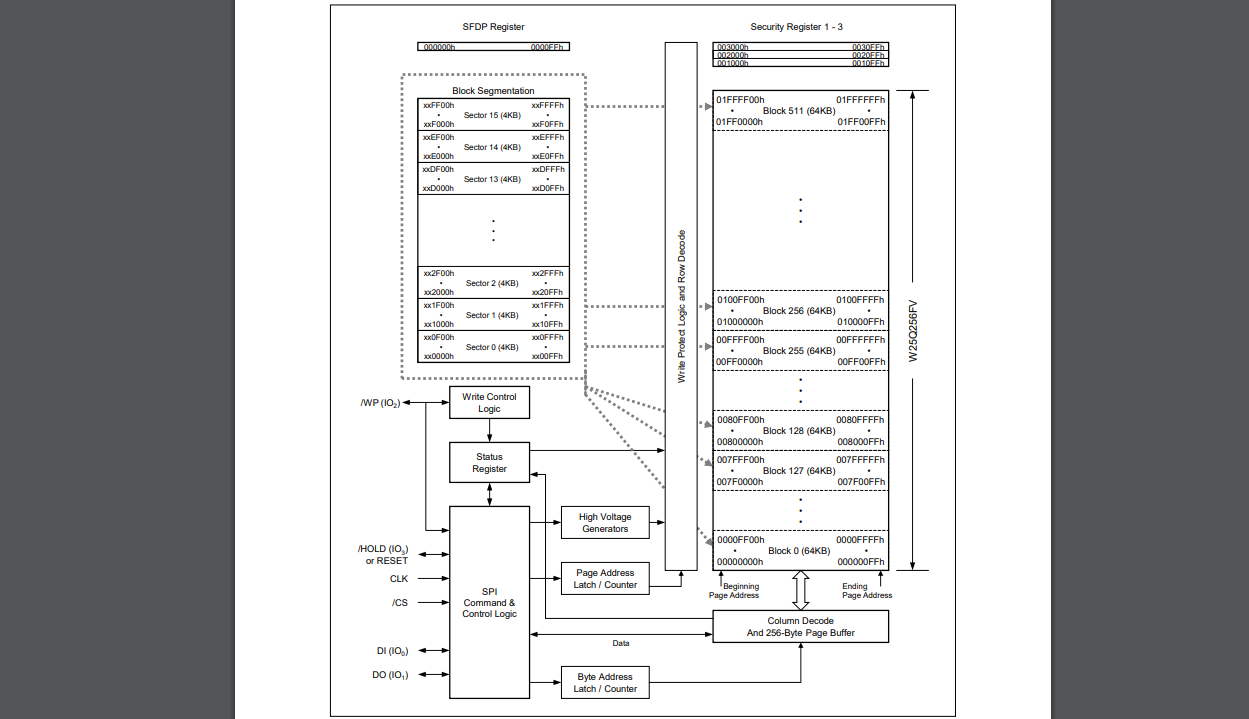

W25Q256FV(256M位)串行闪存为空间、管脚和电源有限的系统提供存储解决方案。25Q系列的灵活性和性能远远超过普通的串行闪存设备。它们非常适合对RAM进行代码跟踪,直接从Dual/Quad SPI(XIP)执行代码,并存储语音、文本和数据。该设备在一个2.7V至3.6V的电源上工作,电流消耗低至4mA激活,1微a断电。所有设备都以节省空间的方式提供。W25Q256FV阵列被组织成131072个可编程页面,每个页面256字节。一次最多可编程256字节。页面可以按16个(4KB扇区擦除)、128个(32KB块擦除)、256个(64KB块擦除)或整个芯片(芯片擦除)分组擦除,W25Q256FV分别有8192个可擦除扇区和512个可擦除块。小的4KB扇区允许在需要数据和参数存储的应用程序中具有更大的灵活性。(见图2.)W25Q256FV支持标准串行外围接口(SPI)、双/四I/O SPI以及双时钟指令周期四外围接口(QPI):串行时钟、芯片选择、串行数据I/O0(DI)、I/O1(DO)、I/O2(/WP)和I/O3(/HOLD)。SPI时钟频率高达104MHz支持在使用快速读取的双/四I/O指令时,允许双I/O的等效时钟频率为208MHz(104MHz x 2),四I/O的等效时钟频率为416MHz(104MHz x 4)。这些传输速率可以优于标准的异步8位和16位并行闪存。连续读取模式允许高效的内存访问,读取24位地址的指令开销只有8个时钟,允许真正的XIP(就地执行)操作。一个保持引脚,写保护引脚和可编程写保护,顶部或底部阵列控制,提供进一步的控制灵活性。此外,该设备支持JEDEC标准制造商、设备ID和SFDP寄存器、64位唯一序列号和三个256字节安全寄存器。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章