资料下载

×

电源噪声和时钟抖动对高速DAC相位噪声有什么样的影响

消耗积分:3 |

格式:pdf |

大小:2.10 MB |

2020-11-18

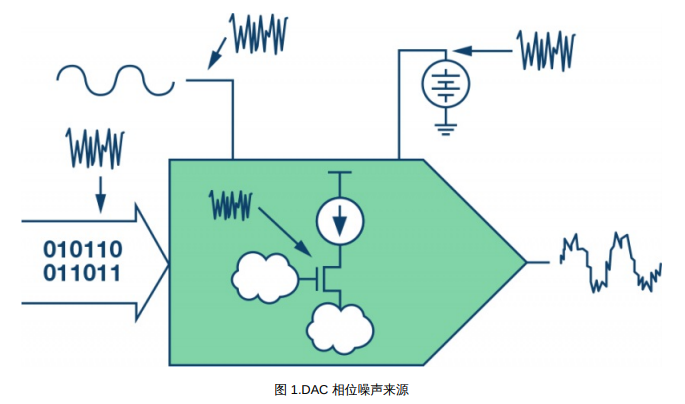

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。这些挑战常常导致一些道听途说的设计规则,并且开发中要反复试错。本文将解决相位噪声问题,目标是通过量化分析来阐明如何围绕高速数模转换器中的相位噪声贡献进行设计。本文旨在获得一种“一次成功”的设计方法,即设计不多不少,刚好满足相位噪声要求。从一块白板开始,首先将 DAC 视作一个模块。噪声可能来自内部,因为任何实际元器件都会产生某种噪声;也可能来自外部噪声源。外部噪声源可通过 DAC 的任何外部的任何外部任意连接,包括电源、时钟和数字接口等,进入其中。图 1 显示了这些可能性。下面将对每一种可能的噪声嫌疑对象分别进行研究,以了解其重要性。

首先讨论数字接口,它恰好是最容易处理的。数字 I/O 负责接收要在模拟域中输出的数字采样信号。众所周知,如眼图所示,数字电路和收到的波形多含噪声。由此看来,相应的问题是:是否所有这种噪声和活动都能渗入 DAC 内部的不同区域且表现为相位噪声?当然,数字接口可能在别处引起噪声,但这里关心的是相位噪声。为了证明 I/O 是否需要关切,我们比较了 AD9162 系列高速 DAC 器件开启和关闭数字接口两种情况下的相位噪声。无数字接口时,器件的 NCO 模式内部生成波形,DAC 事实上变成 DDS 发生器。图 2 显示了实验结果。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章