资料下载

×

基于System Verilog中的随机化激励

消耗积分:0 |

格式:rar |

大小:0.24 MB |

2017-10-31

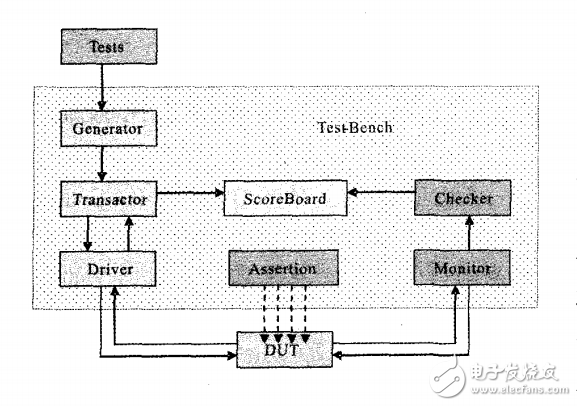

随着电路工艺设计技术的不断发展 ,集成电路的逻辑设计变得越来越复杂 ,随之对验证工作提 出了更高的要求 。由于投片 (tip—out)的费用较高 ,很有必要在投片前对芯片设计进行全面 、可信的验证 ,以尽量减少 “设计——测试——投片——调试——发现 Bug修改设计”这一流程 的迭代次数。因此在集成 电路芯片的设计中 ,尤其是复杂逻辑设计中 ,对测试工作 的效率和可靠性提出了更高的要求。在传统的验证方法中,也有将激励随机化 的方法 ,这样可以用较少的测试代码生成较多 、较全面的测试激励 。这些方法减少了人为因素的干扰 ,能有效地提高验证 的工作效率和可靠性 。在 SystemVerilog中 ,强调在 验证 中使用可重用的验证 IP,包括如何生成 随机化激励 。对于如何尽可能地使用 已有 的验证 IP,以及编写符合标准 的可重用验证组件 ,SystemVerilog提供了一整套 的机制 ,这使得符合规范的随机化激励组件能够很好地在多个设计间复用 ,这更进一步地提高了验证工作的效率和可靠

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章