资料下载

×

高速D/A转换器的宽带输出网络设计解析

消耗积分:1 |

格式:rar |

大小:0.8 MB |

2017-11-15

今天,对于新IC元器件和技术的需求依然以令人吃惊的速度增长。商业和国防工业是需求增长的主要刺激因素。目前涉及半导体行业的大部分新规格都围绕着降低尺寸(size)、重量(weight)和功耗(power)而展开——即SWaP.在半导体行业,我们通过不断改进的技术以及更巧妙的设计来满足这些要求。然而,性能也是关键需求,尤其是GSPS领域的数模转换器(DAC)技术。为了跟上这一步伐,人们常常忽略了关键的模拟输出匹配网络。

为了提供更高的清晰度,通常认为高频是超过1 GHz的频率,高速是超过1 GSPS的速度;更重要的是,最终用户可能会在DAC之后集成一个放大器,因此可用信号便不那么依赖于信号电平,而更多地依赖噪声和保真度。本文将讨论匹配元器件及其互连,并在选择变压器或巴伦,以及涉及到应用连接配置技巧时重点关注关键规格。最后,本文将提供一些思路和优化技巧,说明在GHz区域工作的DAC如何实现宽带平滑阻抗变换。

背景信息

DAC用途广泛,最常见的用途包括:商业和军事通信中的高频复杂波形生成、无线基础设施、自动测试设备(ATE)以及雷达和军用干扰电子产品。系统架构师找到合适的DAC后,必须考虑输出匹配网络,以保持信号结构。元件选型和拓扑较之从前更为重要,因为GSPS DAC应用要求工作在超奈奎斯特频率下,此时所需的频谱信息位于第二、第三或第四奈奎斯特区。

预备知识

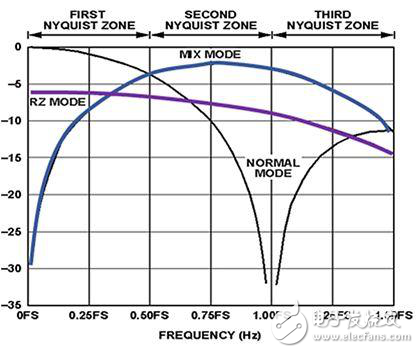

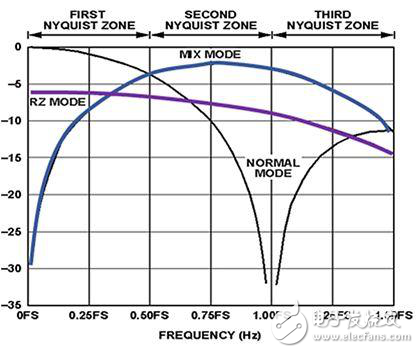

首先让我们来考察DAC的作用,及其在信号链中的位置。DAC的作用很像信号发生器。它能在中心频率(Fc)范围内为复杂波形提供单音。以前,Fc最大值位于第一奈奎斯特区中,或者为采样频率的一半。较新的DAC设计具有内部时钟倍频器,可以有效地倍增第一奈奎斯特区;可将其称为“混频模式”操作。使用混频模式的DAC自然输出频率响应具有sinX/e^(X^2)曲线的形状,如图1所示。

系统架构师可参考产品数据手册,了解元器件性能。很多时候,诸如功率水平和无杂散动态范围(SFDR)等性能参数会给出多种频率下的数值。明智的系统设计人员可将同一个DAC应用于上文所述的超奈奎斯特区中。值得注意的是,在较高频率下(或较高区域中)预期输出电平将会低得多,因此很多信号链会在DAC之后集成一个额外的增益模块或驱动放大器,以补偿该损耗。

图1:DAC Sinx/x输出频率响应与混频模式的关系

元器件方面的考虑,如选择输出巴伦

只有最终用户设计和测得的最佳性能GSPS DAC才是好器件。为了最大程度发挥高品质DAC的性能,应当只选用最好的元器件。必须在一开始就作出重要的电路决定。数据手册上的DAC性能是否提供了足够的输出功率?是否需要有源器件?信号链是否需要从DAC差分输出传送至单端环境?是否需要用到变压器或巴伦?巴伦的合适阻抗比是多少?本文将重点讨论巴伦或变压器的使用。

选择巴伦时,应仔细考虑相位和幅度不平衡1.阻抗比(即电压增益)、带宽、插入损耗和回损同样也是重要的性能考虑因素。采用巴伦进行设计并不总是简单明了。例如,巴伦的特性随频率而改变,这会给预期蒙上阴影。有些巴伦对接地、布局布线和中心抽头耦合敏感。

系统设计人员不应完全根据巴伦数据手册上的性能作为器件选择的唯一基础。经验在这里能够发挥巨大作用:存在PCB寄生效应时,巴伦以新的形式构成外部匹配网络;转换器的内部阻抗(负载)同样成为等式的一部分。

选择巴伦时需注意的重要特性有很多,本文不作深入讨论。

目前市场上,Anaren、Hyperlabs、Marki Microwave、MiniCircuits和Picosecond作为最佳解决方案,可提供最宽的带宽。这些专利设计采用特殊拓扑,允许只采用单一器件实现千兆区域带宽扩展,从而提供更高的平衡度。

使用单个巴伦或多个巴伦拓扑时,最后需要注意的一点是,布局对于相位不平衡同样具有重要作用。为在高频下保持最佳性能,布局应尽可能对称。否则,走线轻微失配可能使采用巴伦的前端设计变得毫无用处,甚至使动态范围受限。

为了提供更高的清晰度,通常认为高频是超过1 GHz的频率,高速是超过1 GSPS的速度;更重要的是,最终用户可能会在DAC之后集成一个放大器,因此可用信号便不那么依赖于信号电平,而更多地依赖噪声和保真度。本文将讨论匹配元器件及其互连,并在选择变压器或巴伦,以及涉及到应用连接配置技巧时重点关注关键规格。最后,本文将提供一些思路和优化技巧,说明在GHz区域工作的DAC如何实现宽带平滑阻抗变换。

背景信息

DAC用途广泛,最常见的用途包括:商业和军事通信中的高频复杂波形生成、无线基础设施、自动测试设备(ATE)以及雷达和军用干扰电子产品。系统架构师找到合适的DAC后,必须考虑输出匹配网络,以保持信号结构。元件选型和拓扑较之从前更为重要,因为GSPS DAC应用要求工作在超奈奎斯特频率下,此时所需的频谱信息位于第二、第三或第四奈奎斯特区。

预备知识

首先让我们来考察DAC的作用,及其在信号链中的位置。DAC的作用很像信号发生器。它能在中心频率(Fc)范围内为复杂波形提供单音。以前,Fc最大值位于第一奈奎斯特区中,或者为采样频率的一半。较新的DAC设计具有内部时钟倍频器,可以有效地倍增第一奈奎斯特区;可将其称为“混频模式”操作。使用混频模式的DAC自然输出频率响应具有sinX/e^(X^2)曲线的形状,如图1所示。

系统架构师可参考产品数据手册,了解元器件性能。很多时候,诸如功率水平和无杂散动态范围(SFDR)等性能参数会给出多种频率下的数值。明智的系统设计人员可将同一个DAC应用于上文所述的超奈奎斯特区中。值得注意的是,在较高频率下(或较高区域中)预期输出电平将会低得多,因此很多信号链会在DAC之后集成一个额外的增益模块或驱动放大器,以补偿该损耗。

图1:DAC Sinx/x输出频率响应与混频模式的关系

元器件方面的考虑,如选择输出巴伦

只有最终用户设计和测得的最佳性能GSPS DAC才是好器件。为了最大程度发挥高品质DAC的性能,应当只选用最好的元器件。必须在一开始就作出重要的电路决定。数据手册上的DAC性能是否提供了足够的输出功率?是否需要有源器件?信号链是否需要从DAC差分输出传送至单端环境?是否需要用到变压器或巴伦?巴伦的合适阻抗比是多少?本文将重点讨论巴伦或变压器的使用。

选择巴伦时,应仔细考虑相位和幅度不平衡1.阻抗比(即电压增益)、带宽、插入损耗和回损同样也是重要的性能考虑因素。采用巴伦进行设计并不总是简单明了。例如,巴伦的特性随频率而改变,这会给预期蒙上阴影。有些巴伦对接地、布局布线和中心抽头耦合敏感。

系统设计人员不应完全根据巴伦数据手册上的性能作为器件选择的唯一基础。经验在这里能够发挥巨大作用:存在PCB寄生效应时,巴伦以新的形式构成外部匹配网络;转换器的内部阻抗(负载)同样成为等式的一部分。

选择巴伦时需注意的重要特性有很多,本文不作深入讨论。

目前市场上,Anaren、Hyperlabs、Marki Microwave、MiniCircuits和Picosecond作为最佳解决方案,可提供最宽的带宽。这些专利设计采用特殊拓扑,允许只采用单一器件实现千兆区域带宽扩展,从而提供更高的平衡度。

使用单个巴伦或多个巴伦拓扑时,最后需要注意的一点是,布局对于相位不平衡同样具有重要作用。为在高频下保持最佳性能,布局应尽可能对称。否则,走线轻微失配可能使采用巴伦的前端设计变得毫无用处,甚至使动态范围受限。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章