资料下载

×

基于门控时钟的低功耗时序电路设计解析

消耗积分:0 |

格式:rar |

大小:0.4 MB |

2017-11-15

在传统设计中,所有计算机运算(算法、逻辑和存储进程)都参考时钟同步执行,时钟增加了设计中的时序电路数量。在这个电池供电设备大行其道的移动时代,为了节省每一毫瓦(mW)的功耗,厂商间展开了残酷的竞争,因此将电路分成多个电源域并根据要求关闭它们,并且在设计每个时序电路的同时节省功耗,这两点至关重要。时序电路(如计数器和寄存器)在现代设计中无处不在。本文以约翰逊计数器为例介绍了如何采用有效门控时钟来设计高能效的时序电路。

约翰逊计数器系统,可同步提供多种特殊类型的数据序列,这对于大多数重要应用(如D/A转换器、FSM和时钟分频器)来说至关重要。为支持不同频率(从MHz到GHz)的模块,越来越多的IP集成到片上系统,因此,设计中在不同层级实施了许多可支持多个分频因子的时钟分频器。本文中,我们介绍了一款节能设计,即用带有门控时钟的多级可编程约翰逊计数器系统来取代多个时钟分频器,该计数器可提供8至任何偶数值(在本文中为38)的时钟分频因子。下面,我们将探讨实施细节和该技术的优劣。

典型时序电路

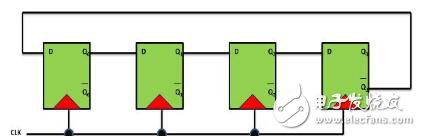

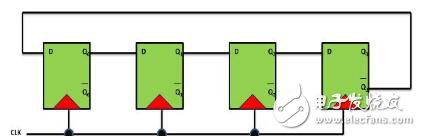

图1给出的是一款传统4位上升沿约翰逊计数器。约翰逊计数器只不过是修改过的移位寄存器,其最后一个D触发器的反相输出作为第一个D触发器的输入。所有其他触发器将接收上一个触发器所提供的输出。

图1 传统约翰逊计数器

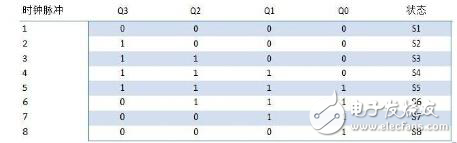

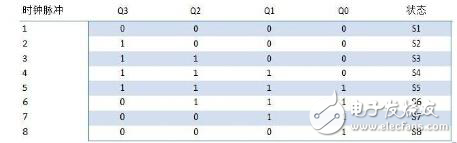

如表1所示,在所有的纵列中,4个连续的“0”后面都跟随着4个连续的“1”,但所有纵列都位于不同的阶段。约翰逊计数器可同步创建一个特定的数据模式。该数据模式在建模时非常有用,因为它可以使用任何抽头就可以产生一个有不同阶段的时钟样式的模式。此外,从表中可以推导出,约翰逊计数器只使用了N个触发器提供2N个状态,因此,与标准环形计数器相比,约翰逊计数器仅需要一半数量的触发器便可实现同样的MOD.

表1 约翰逊计数器的状态图

典型时序电路的缺陷

如图1所示,这种电路最大的缺点是不可配置,因此,不能改变时钟分频因子。一个N触发器设计只能产生2N个周期的时钟。需要预先将固定数量的触发器加入到设计中,才能产生固定周期的时钟。这大大阻碍了特定时钟的设计,而且多个这样的设计,需要多种分频因子来进行分频。

另外,该设计非常耗能,并且也没有机制可通过高效门控时钟来节省动态功耗。如表1所示,Q3只能在时钟脉冲2和时钟脉冲6中改变其输出,对于所有其他时钟而言,触发器一次又一次地存储了相同的数据。这导致在时钟周期内产生了不必要的功耗,而采用适合的门控时钟可解决该问题。

约翰逊计数器系统,可同步提供多种特殊类型的数据序列,这对于大多数重要应用(如D/A转换器、FSM和时钟分频器)来说至关重要。为支持不同频率(从MHz到GHz)的模块,越来越多的IP集成到片上系统,因此,设计中在不同层级实施了许多可支持多个分频因子的时钟分频器。本文中,我们介绍了一款节能设计,即用带有门控时钟的多级可编程约翰逊计数器系统来取代多个时钟分频器,该计数器可提供8至任何偶数值(在本文中为38)的时钟分频因子。下面,我们将探讨实施细节和该技术的优劣。

典型时序电路

图1给出的是一款传统4位上升沿约翰逊计数器。约翰逊计数器只不过是修改过的移位寄存器,其最后一个D触发器的反相输出作为第一个D触发器的输入。所有其他触发器将接收上一个触发器所提供的输出。

图1 传统约翰逊计数器

如表1所示,在所有的纵列中,4个连续的“0”后面都跟随着4个连续的“1”,但所有纵列都位于不同的阶段。约翰逊计数器可同步创建一个特定的数据模式。该数据模式在建模时非常有用,因为它可以使用任何抽头就可以产生一个有不同阶段的时钟样式的模式。此外,从表中可以推导出,约翰逊计数器只使用了N个触发器提供2N个状态,因此,与标准环形计数器相比,约翰逊计数器仅需要一半数量的触发器便可实现同样的MOD.

表1 约翰逊计数器的状态图

典型时序电路的缺陷

如图1所示,这种电路最大的缺点是不可配置,因此,不能改变时钟分频因子。一个N触发器设计只能产生2N个周期的时钟。需要预先将固定数量的触发器加入到设计中,才能产生固定周期的时钟。这大大阻碍了特定时钟的设计,而且多个这样的设计,需要多种分频因子来进行分频。

另外,该设计非常耗能,并且也没有机制可通过高效门控时钟来节省动态功耗。如表1所示,Q3只能在时钟脉冲2和时钟脉冲6中改变其输出,对于所有其他时钟而言,触发器一次又一次地存储了相同的数据。这导致在时钟周期内产生了不必要的功耗,而采用适合的门控时钟可解决该问题。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章