资料下载

×

基于多CPU架构伺服驱动控制器的研究

消耗积分:3 |

格式:rar |

大小:1.14 MB |

2018-01-29

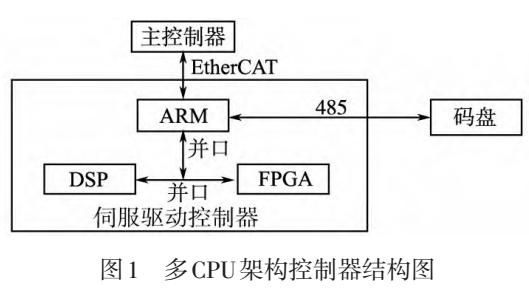

伺服驱动器是用来控制伺服电机的一种控制器,一般是通过位置、速度和力矩3种方式对电机进行控制,实现高精度的系统定位。目前,伺服控制器CPU的架构主要有:1)单CPU架构ARM( acorn RISC machine)控制器;2)单CPU架构DSP(digital signal process)控制器;3)ARM+FPGA+DSP架构的多CPU控制器。方法3)是目前最先进的架构,前2种方法都有局限陛。方法1)和方法2)采用单CPU架构的控制器,一个CPU集算法、采集控制、通讯、显示功能于一体,当算法复杂度和实时性要求高时往往会顾此失彼。而方法3)的架构中各CPU分T明确,ARM负责通信和显示功能,DSP负责算法运算,FPGA负责采集和控制。方法3)的技术瓶颈是满足伺服控制器的实时性要求需要几个CPU之间的高速数据通信,因此,如果能够找到一个高速的通信方式完全可以发挥各个CPU的特性,就像一个多核CPU在工作一样。

本研究基于ARM+FPGA+DSP架构,采用并口通信的方法用于几个CPU之间的内部高速通信。此外,伺服驱动器作为伺服系统的一部分还需要和主控器和编码器进行高速通信,来满足整个伺服系统的实时性要求。本架构采用EtherCAT和高速485接口用于控制器和其他设备进行高速通信,描述了系统的原理架构和软件设计架构。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章