资料下载

×

基于4通道时间交织的FPGA高速模数转换采样系统

消耗积分:3 |

格式:rar |

大小:0.55 MB |

2018-02-07

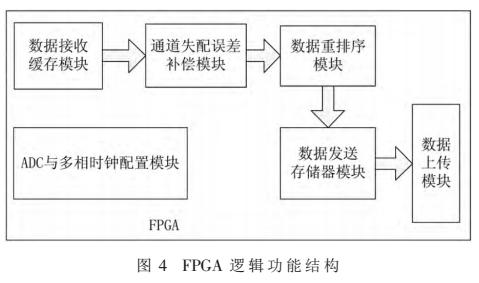

高性能的模数转换器(Analog Digilal Convertei.ADC)被广泛应用于通信、仪器仪表、计算机和医疗设备等领域,对国民经济、国防建设以及科学研究具有重要意义。单采样单元的ADC芯片由于存在内部热噪声、孔径抖动和渡越时间不确定性等因素,面临采样速度和精度相互制约的影响,出现了瓶颈。而由多通道时间交织ADC(Time-lnterleaved ADC.TIADC)采用M个相同型号的ADC单元依次交替完成采样。理论上,TIADC的采样率可以到达单ADC的M倍,同时保持采样精度基本不变。但是由于ADC采样单元与外围电路的个体差异,导致的采样通道间不一致性会引起失配失真,如偏置误差、增益误差以及时间相位误差将严重降低数据采集系统性能。基于数字信号处理方法的数字后端修正技术可有效抑制以上失配造成的失真。近年来,已有文献应用FPCJA实现数字后端修正技术。

本文提出并设计了一套4通道时间交织FPCJA高速模拟信号采样系统。系统的数据流挖制、失配误差数字修正等功能均在l片FPCJA中实现,无需额外采用DSP处理器,降低了系统的结构复杂度。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章