PLL控制器和分辨率模式切换详解

Altera公司锁相环IP核介绍

Texas Instruments CDC536:高性能时钟驱动器的深度剖析

Texas Instruments CDCU877/CDCU877A:高性能时钟驱动器的卓越之选

CDCE906:高性能可编程时钟合成器的深度解析

CDCE706:高性能3 - PLL时钟合成器的深度解析

SyncE/IEEE1588/DPLL时钟净化器为什么更依赖VCXO?

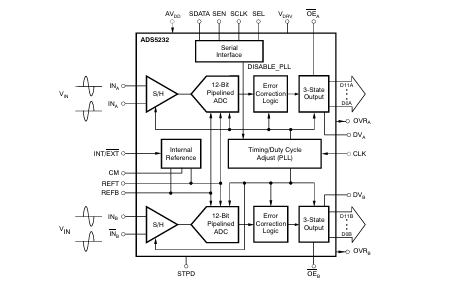

德州仪器ADS5232:高性能12位ADC的深度剖析

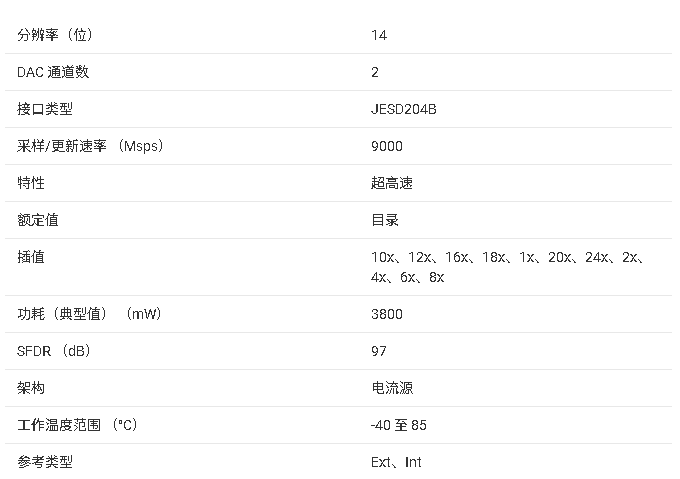

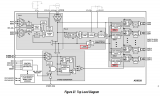

DAC38RF82 双通道、14位、9GSPS、1x-24x插值、6 和 9 GHz PLL 数模转换器技术手册

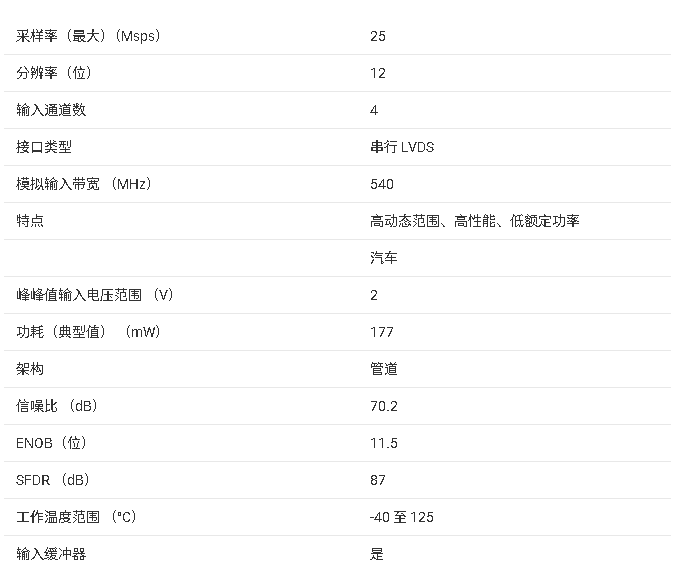

ADC3421-Q1 汽车四通道 12 位 25MSPS 模数转换器

AFE159x系列低功耗生物电位测量模拟前端技术文档总结

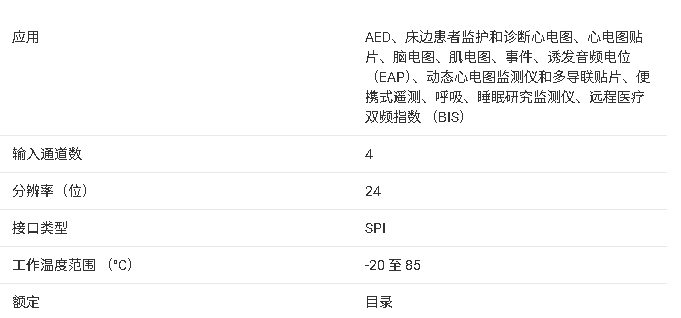

AFE159P4数据手册完整总结

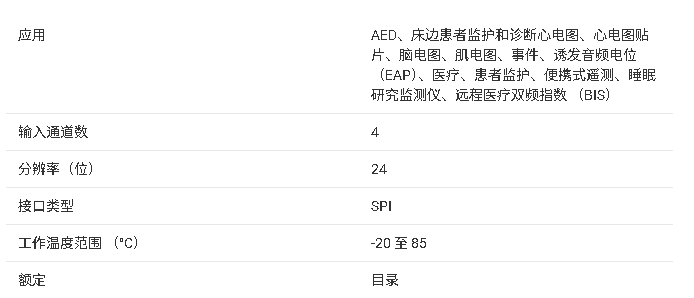

AFE159x系列数据手册完整总结

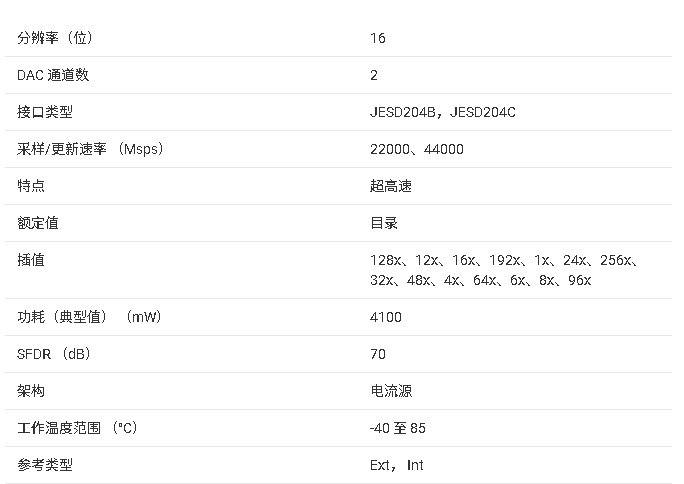

DAC39RF20核心信息总结

AD9528双级PLL的时钟分布特性

【FPGA 开发分享】如何在 Vivado 中使用 PLL IP 核生成多路时钟

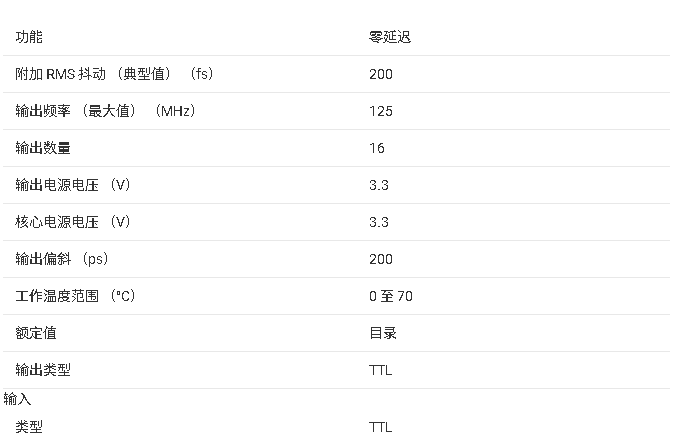

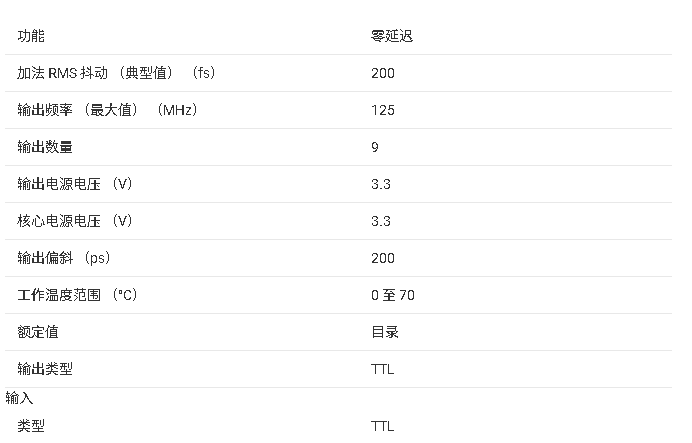

CDC2536 锁相环时钟驱动器技术文档总结

CDC536 3.3V锁相环时钟驱动器技术文档总结

CDC516 3.3V相位锁定环时钟驱动器技术文档总结

CDC509 3.3V相位锁定环时钟驱动器技术文档总结