资料下载

Verilog HDL的经典练习题免费下载

1. 产生一个高电平持续时间和低电平持续时间分别为3 ns和10 ns的时钟。

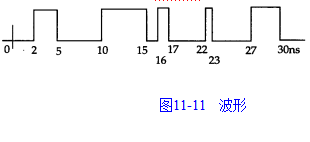

2. 编写一个产生图11 - 11所示波形的Verilog HDL模型。

3. 产生一个时钟C l o c k V,该时钟是模块G e n C l k D中描述的时钟C l k D(如图11 - 6所示)的相移时钟,相位延迟为15 ns 。[提示:用连续赋值语句可能会不合适。]

4. 编写测试时序检测器的测试验证程序。时序列检测器按模式1 0 0 1 0在每个时钟正沿检查输入数据流。如果找到该模式,将输出置为1;否则输出置为0。

5. 编写一个模块生成两个时钟, C l o c k A和C l o c k B。C l o c k A 延迟10 ns后有效,C l o c k B延迟4 0n s后有效。两个时钟有相同的高、低电平持续时间,高电平持续时间为1 ns,低电平持续时间为2 n s。C l o c k B与时钟C l o c k A边沿同步,但极性相反。

6. 描述4位加法/减法器的行为模型。用测试验证模块测试该模型。在测试验证模块内描述所有输入激励及其期望的输出值。将输入激励、期望的输出结果和监控输出结果转储到文本文件中。

7. 描述在两个4位操作数上执行所有关系操作(《, 《=, 》, 》=)的A L U。编写一个从文本文件中读取测试模式和期望结果的测试验证模块。

8. 编写一个对输入向量作算术移位操作的模块。指定输入长度用参数表示,缺省值为3 2。同时指定移位次数用参数表示,缺省值为1。编写一个模拟、测试模块以验证对1 2位向量进行8次移位算术操作的正确性。

9. 编写N倍时钟倍频器模型。输入是频率未知的参考时钟。输出时钟的倍数与参考时钟的每个正沿同步。[提示:确定参考时钟的时钟周期。

10. 编写一个模型,显示输入时钟每次由0转换到1的时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章