资料下载

×

基于74LS162数字钟的设计与实现及其时间校准的研究

消耗积分:0 |

格式:rar |

大小:1.2 MB |

2017-11-27

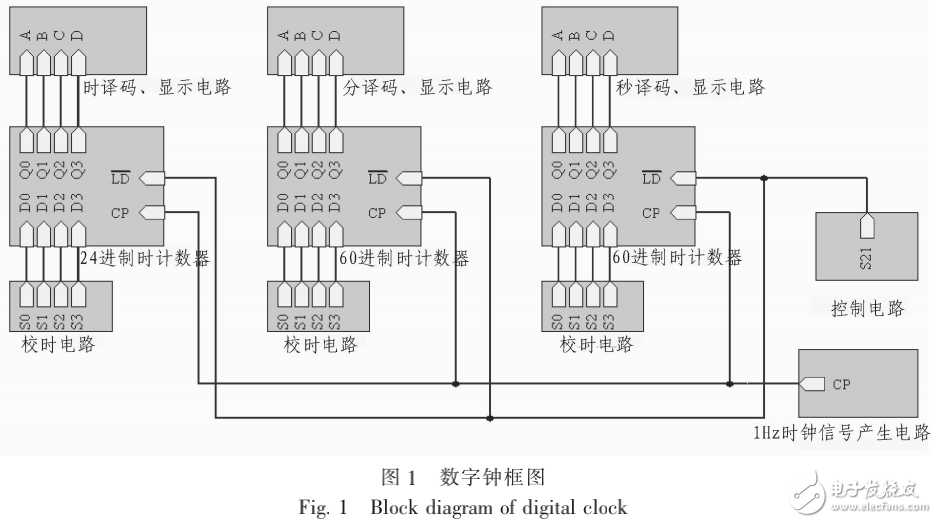

数字钟电路一般设有校时功能。本文基于不截断正常的计数通路和加入校时脉冲信号对数字钟进行校时,采用了将所有计数器芯片74LS162的计数时钟输入端CP端均接同一个CP信号、将所有计数器芯片的置数端连在一起的方法。所设计的电路仅通过开关的接通或断开便可调整数字钟的时间值,而且时、分、秒的校时操作是任意的和互不干扰的。电路的设计能对秒的时间值进行调整,时钟精确度高。

60进制分钟和秒钟计时电路

通常,数字钟的分钟和秒钟计时电路要设计为60进制计数器。如图2所示,是分钟和秒钟计时电路,分别用两个74LS162芯片构成60进制计数器。它们的个位芯片接成十进制形式,个位在1 Hz CP信号上升沿作用下按照842IBCD码进行加法计数…,将此块芯片的进位输出端“TC”联接到十位芯片的使能端“CEP”和“CET”,此联接实现“逢十进一”的功能。十位芯片的设置非常重要,它要求有“60进1”的功能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章