资料下载

×

采用可配置逻辑单元(CLC)实现无毛刺设计的详细中文资料概述

消耗积分:2 |

格式:pdf |

大小:1.63 MB |

2018-05-25

数字电路设计人员经常面临的挑战之一是要消除所设计电路的毛刺信号。为此,通常需要确保数据锁存期间具有足够的建立时间以及保持时间。

“毛刺”是不能在整个时钟周期内都保持有效的信号。带毛刺的信号如果馈送至多个锁存器的时钟线,部分锁存器可能无法更新。这无疑是设计人员要避免的情况。

还应当注意传播延时会随温度而变化,因此,开发期间未产生毛刺的设计电路在其他情况下仍有可能产生毛刺。

Microchip的外设集增加了可配置逻辑单元(Configurable Logic Cell,CLC),使最终用户能够从根本上“设计”可与 PIC® 单片机接口的简单外设。CLC 外设能将信号驱动至 PIC 器件,但可能引起中断和计数器递增,因此有必要提供一些指导意见,以通过该外设实现稳定的设计。

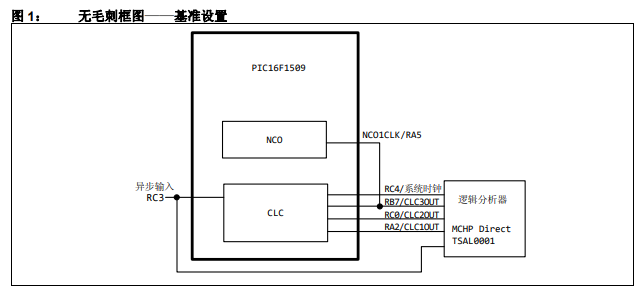

本示例采用了 PIC16F1509,并且使用了 4 个可用 CLC 模块中的 3 个。第 4 个 CLC 模块用于将内部 FOSC 连接至 RC4 引脚,以便通过逻辑分析器来查看该信号。其他 CLC 内部信号 (XOR 输出和锁存器输出)则连接至外部引脚,以便能更直观地了解应用的工作原理。

如下框图(图 1)所示,RC3 引脚上为异步输入信号, CLC 输出馈送至逻辑分析器。CLC3 信号为无毛刺时钟信号,馈入至 NCO1CLK 焊盘。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章