资料下载

×

74HC573锁存器和单片机的周期详细资料概述

消耗积分:1 |

格式:pdf |

大小:0.09 MB |

2019-04-23

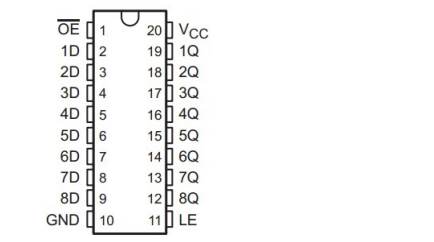

这是74HC573 锁存器的引脚分布图,OE的专业术语为三态允许控制端(低电平有效),通常叫作输出使能端,或者输出允许端都可以; 1D~8D 为数据输入端;1Q~8Q为数据输出端; LE为锁存允许端,或叫锁存控制端。

上图为74HC573的真值表。真值表用来表示数字电路或者数字芯片工作状态的直观特性。 真值表中字母的含义 H--高电平 、 L--低电平 、 X--任意电平 、Z--高阻态 也就是既不是高电平也不是低电平,而它的电平状态由与它相连接的其他电气状态决定; Q0--上次的电平状态。由图可看出,当OE为高电平时,无论LE与D端为何种电平状态,其输出都为高阻态。很明显,此时该芯片处于不可控制状态。

而我们将74HC573接入电路是必须要控制它的,由此在设计电路时就必须将OE接低电平。所以在TX-1C开发板上使用的三个锁存器的OE端全部接地。当OE为低电平时,LE为H时,D与Q同时为H或L; 而当LE为L时,无论D保持何种电平状态,Q都保持上一次的数据状态。也就是说,当LE为高电平时,Q端数据紧随D端数据而变化;当LE为低电平时Q端数据保持LE端变化为低电平之前Q端的数据状态。在开发板上,LE端与单片机的引脚相连,再将锁存器的输入端与单片机的的某组I/O口相连,便可通过控制锁存器的锁存端与锁存器的数据输入端的数据来改变锁存器的数据输出端的数据状态。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

评论(0)

发评论

- 相关下载

- 相关文章