资料下载

ad9550用于有线通信的整数N时钟转换器

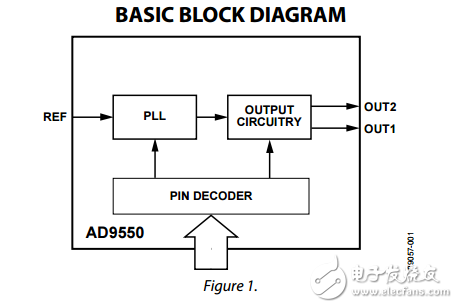

The AD9550 is a phase-locked loop (PLL) based clock translator designed to address the needs of wireline communication and base station applications. The device employs an integer-N PLL to accommodate the applicable frequency translation requirements. It accepts a single-ended input reference signal at the REF input. The AD9550 is pin programmable, providing a matrix of standard input/output frequency translations from a list of 15 possible input frequencies to a list of 52 possible output frequency pairs (OUT1 and OUT2)。 The AD9550 output is compatible with LVPECL, LVDS, or single-ended CMOS logic levels, although the AD9550 is implemented in a strictly CMOS process. The AD9550 operates over the extended industrial temperature range of −40°C to +85°C.

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章