资料下载

基于PCM采编器的VerilogHDL语言设计

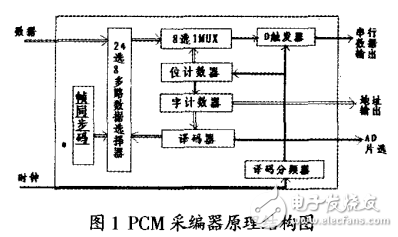

微电子技术和计算机技术的飞速发展,使得现代电子系统的设计和应用进入了—个全新的时代。系统芯片 SOC(System OnChip)从—个概念变成为现实,EDA技术已成为支撑电子设计的通用平台,并走向支持系统级的设计发展 I]。Ver—ilogHDL是 一种在 C语言基础上发展起来的优秀的硬件描述语言,在 ASIC设计领域 占据了主导地位。VerilogHDL作为一种通用的标准 EDA设 汁语言,在设计电子系统中有着广泛的应用。其中 PCM采编器就是一例。2PCM采编器的组成工作原理PCM采编器是一种常用的数字部件 ,主要用于遥测数据采集、格式打包和信源压缩编码等。然界和生活中的图象和声音都 是连续变化无间断的模拟信号,而数字信号在时间、空间上都是离散的,要想进行数字化传输,必须先转化成为数字信号。简单地讲,其过程就是在符合抽样定理的前提下,对模拟图象和声音采样,再将时间离散化的信号按一定的量化间隔量化 ,完成幅度的离散化,然后 以特定规则编码 ,最种形成数字信号。这就是信源数字编码的过程。但此时的信号码率过高(数字复 合 NTSC为 143Mbp8,数 字 复 合 PAL为177MbpS,数字分量 ITu—R601为 216MbpS(8比 特 )或 270MbpS (10 比特 ),立 体 声 为1-SMbpS),要经过压缩后方可能在给定的带宽内传输。信源压缩编码的目的就是去除信源中的冗余成分,提高传输效率。PCM采编器将采集来的数据加上同步码 ,形成一定的帧格式 ,再进行并/串转换,形成 串行数据流送到其他的设备。PCM 采编器的结构如图 1PCM采编器的帧格式 :帧长为 128字节 ,长为 8位,码率为 500kb/s,地址分配为:帧同步码0,1路 ;模拟通道:2-100路;数字通道 :101~127路;帧同步码为 :EB9

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。 举报投诉

- 相关下载

- 相关文章